You are here:

HSIC USB 2.0 PHY IP

The USB 2.0 HSIC PHY IP is a cost effective and lower power replacement for a standard USB 2.0 PHY in applications where USB is being used on a single printed circuit board. It is becoming increasingly attractive to use USB as a high speed chip-to-chip interconnect within a product where low cost and low power are required. However, because USB was designed to enable hot-plugging of peripherals over cables up to 5 meters in length, certain power and implementation features are not required for chip-to-chip interconnect solutions. To better meet the needs of a USB chip-to-chip interconnect, HSIC accomplishes this by removing the analog transceivers, thus reducing complexity, cost and manufacturing risk.

查看 USB HSIC PHY - High Speed Inter-Chip IP Core 详细介绍:

- 查看 USB HSIC PHY - High Speed Inter-Chip IP Core 完整数据手册

- 联系 USB HSIC PHY - High Speed Inter-Chip IP Core 供应商

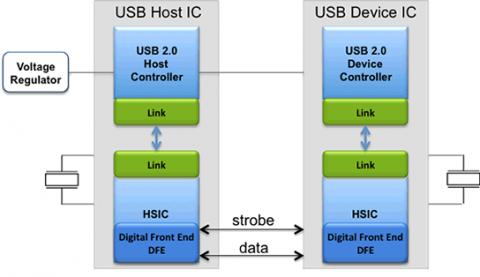

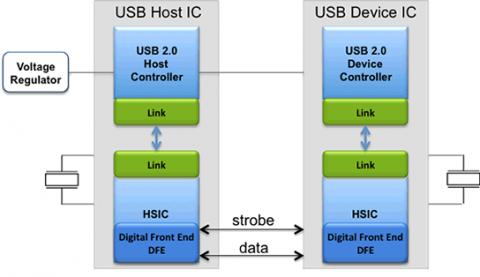

Block Diagram of the USB HSIC PHY - High Speed Inter-Chip IP Core

usb phy IP

- USB 2.0 PHY TSMC 5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm, 65nm, 130nm, 180nm

- USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- USB 2.0 OTG High / Full / Low- Speed Dual Role IP Core

- USB 3.1 PHY (10G/5G) inTSMC (16nm, 12nm, N7, N6, N5,N3E, N3P)

- USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in TSMC 22ULP