You are here:

USB 3.0/ PCIe 2.0 Combo PHY IP,在 TSMC 28HPC+ 中经过硅验证

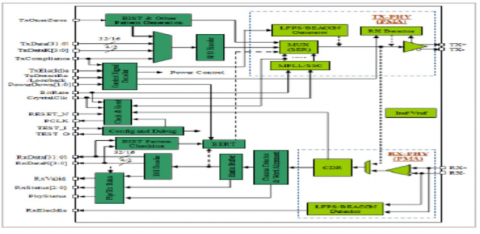

这个Combo PHYIP是完整的USB 3.0和PCIe 2.0 PHY IP解决方案,专为TSMC 28nm过程中的移动和数据消费者应用而设计。这个IP同时支持USB3.0 (1个或2个端口)和PCIe 2.0 (1个通道),由物理编码子层和物理媒体附件组成,包括所有用于8/10编码/解码、驱动器、输入缓冲器、PLL和阻抗匹配电路。这个PHY IP提供了具有媒体访问层的标准管道接口,用于交换信息。这个PHY IP通过额外的PLL控制、参考时钟控制和嵌入式电源门控控制,实现了低功耗。此外,上述低功率模式设置是可配置的,这个PHY IP广泛适用于在不同的功耗考虑下的各种场景.

查看 USB 3.0/ PCIe 2.0 Combo PHY IP,在 TSMC 28HPC+ 中经过硅验证 详细介绍:

- 查看 USB 3.0/ PCIe 2.0 Combo PHY IP,在 TSMC 28HPC+ 中经过硅验证 完整数据手册

- 联系 USB 3.0/ PCIe 2.0 Combo PHY IP,在 TSMC 28HPC+ 中经过硅验证 供应商

Block Diagram of the USB 3.0/ PCIe 2.0 Combo PHY IP,在 TSMC 28HPC+ 中经过硅验证

USB 3.0combo PHY IP

- USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in TSMC 22ULP

- USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in TSMC 28HPC+

- USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in SMIC 40LL

- USB 3.0/ PCIe 3.0/ SATA 3.0 Combo PHY IP, Silicon Proven in SMIC 14SF+

- USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in SMIC 55LL

- USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in SMIC 28SF