You are here:

USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm

The Arasan USB 2.0 PHY IP core is a transceiver compliant with the USB 2.0 Transceiver Macrocell Interface Plus (UTMI+) level 3 specification, for use with host, embedded host, On-the-Go (OTG) and function controllers. Its high speed, mixed-signal circuitry supports 480 Mb/s USB 2.0 High Speed (HS) traffic, while remaining backward compatible with USB 1.1 legacy protocol for 12Mb/s Full Speed (FS) traffic and 1.5Mb/s Low Speed (LS) traffic.

The USB 2.0 PHY performs low-level protocol and signaling functions. While transmitting, the PHY serializes data, generates Synchronize (SYNC) and End-of-Packet (EOP) packet fields, and performs bit stuffing and Non-Return-to-Zero Inverted (NRZI) encoding. While receiving data, the PHY recovers incoming data and clock, de-serializes data, strips SYNC and EOP fields, and performs bit un-stuffing and NRZI decoding.

The USB 2.0 PHY is a full-featured on-chip physical transceiver. It has Electro Static Discharge (ESD) protection and fully supports all OTG and host functionality. An optional charge pump generates a 5V supply to power external USB peripherals while in host mode. On-board clock generation and PLL blocks provide for accurate, high-speed data transmission from and to the transceiver. When this USB PHY core is used, a minimal number of external components is required.

Arasan’s USB 2.0 PHY IP is also offered as a crystal-less PHY saving on the BoM.

The USB 2.0 PHY performs low-level protocol and signaling functions. While transmitting, the PHY serializes data, generates Synchronize (SYNC) and End-of-Packet (EOP) packet fields, and performs bit stuffing and Non-Return-to-Zero Inverted (NRZI) encoding. While receiving data, the PHY recovers incoming data and clock, de-serializes data, strips SYNC and EOP fields, and performs bit un-stuffing and NRZI decoding.

The USB 2.0 PHY is a full-featured on-chip physical transceiver. It has Electro Static Discharge (ESD) protection and fully supports all OTG and host functionality. An optional charge pump generates a 5V supply to power external USB peripherals while in host mode. On-board clock generation and PLL blocks provide for accurate, high-speed data transmission from and to the transceiver. When this USB PHY core is used, a minimal number of external components is required.

Arasan’s USB 2.0 PHY IP is also offered as a crystal-less PHY saving on the BoM.

查看 USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm 详细介绍:

- 查看 USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm 完整数据手册

- 联系 USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm 供应商

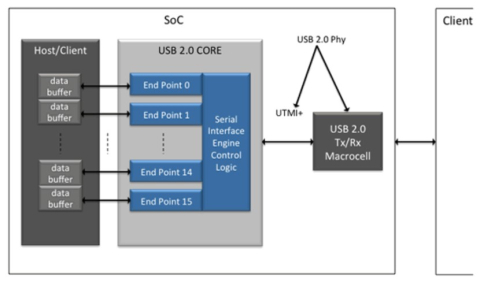

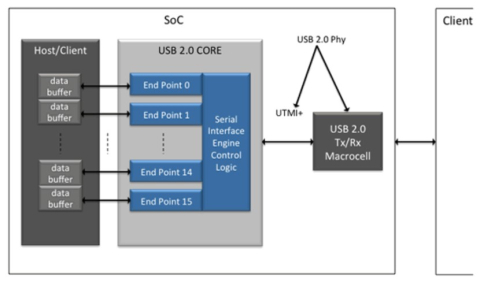

Block Diagram of the USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm

USB PHY IP

- USB 2.0 PHY TSMC 5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm, 65nm, 130nm, 180nm

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- USB 2.0 OTG High / Full / Low- Speed Dual Role IP Core

- USB 3.1 PHY (10G/5G) inTSMC (16nm, 12nm, N7, N6, N5,N3E, N3P)

- USB 3.0/ PCIe 2.0/ SATA 3.0 Combo PHY IP, Silicon Proven in TSMC 22ULP

- USB 2.0 PHY IP, Silicon Proven in TSMC 22ULP