You are here:

USB 2.0 Hub Controller

The Arasan USB 2.0 Hub IP core is an USB 2.0 specification compliant hub core

that supports 480 Mbit/s in High Speed (HS) mode, 12 Mbit/s in Full Speed (FS)

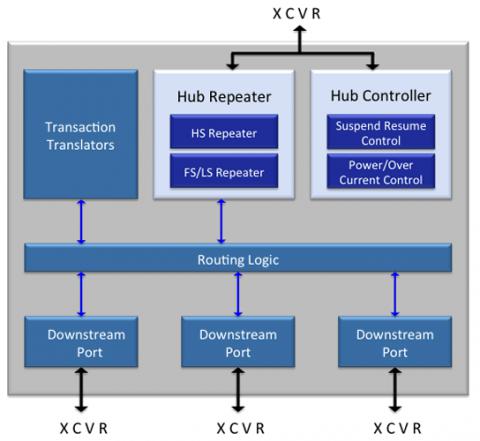

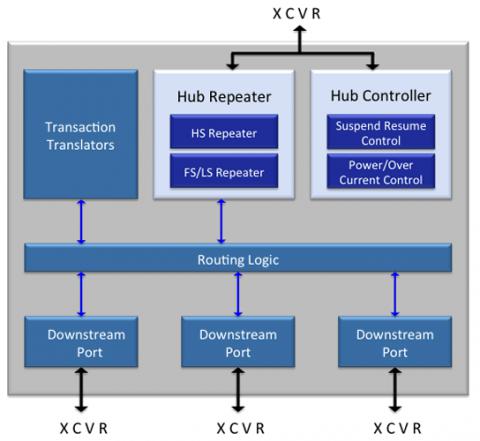

mode, and 1.5 Mbit/s in Low Speed (LS) mode. The Arasan USB 2.0 Hub IP core consists of the Hub Controller, Hub Repeater, Transaction Translators, Routing Logic, and Downstream Ports.

The Hub Controller controls the operation of the USB hub by interpreting both the USB commands and Hub class specific commands. High-speed packets originated from the root hub are forwarded by the Hub Repeater to the HS Downstream Ports through the Routing Logic. Full-speed and low-speed packets scheduled by the host system software as split transactions are forwarded to the Transaction Translators. The Transaction Translators handle split transactions that convey isochronous, interrupt, control, and bulk transfers across the high-speed bus to and from the full-speed and low-speed devices that attached to the hub. The Transaction Translators also perform CRC on incoming packets from the Hub Repeater or Routing Logic. The Routing Logic connects the Hub Repeater to the Downstream Ports in a high-speed transfer, and it connects the Transaction Translators to the Downstream Ports in a full-speed or low-speed transfer. The number of Downstream Ports is scalable.

The Arasan Auto-configure and Auto-wire are pre-compiled C language utilities that allow users to have the freedom to fully customize their designs.

that supports 480 Mbit/s in High Speed (HS) mode, 12 Mbit/s in Full Speed (FS)

mode, and 1.5 Mbit/s in Low Speed (LS) mode. The Arasan USB 2.0 Hub IP core consists of the Hub Controller, Hub Repeater, Transaction Translators, Routing Logic, and Downstream Ports.

The Hub Controller controls the operation of the USB hub by interpreting both the USB commands and Hub class specific commands. High-speed packets originated from the root hub are forwarded by the Hub Repeater to the HS Downstream Ports through the Routing Logic. Full-speed and low-speed packets scheduled by the host system software as split transactions are forwarded to the Transaction Translators. The Transaction Translators handle split transactions that convey isochronous, interrupt, control, and bulk transfers across the high-speed bus to and from the full-speed and low-speed devices that attached to the hub. The Transaction Translators also perform CRC on incoming packets from the Hub Repeater or Routing Logic. The Routing Logic connects the Hub Repeater to the Downstream Ports in a high-speed transfer, and it connects the Transaction Translators to the Downstream Ports in a full-speed or low-speed transfer. The number of Downstream Ports is scalable.

The Arasan Auto-configure and Auto-wire are pre-compiled C language utilities that allow users to have the freedom to fully customize their designs.

查看 USB 2.0 Hub Controller 详细介绍:

- 查看 USB 2.0 Hub Controller 完整数据手册

- 联系 USB 2.0 Hub Controller 供应商

Block Diagram of the USB 2.0 Hub Controller

interface controllers and phy IP

- Globalfoundries 12nm MIPI D-PHY V1.2@2.5GHz

- 1.6T Ultra Ethernet IP Solution with PHY, Controller and Verification IP

- USB 2.0 PHY TSMC 5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm, 65nm, 130nm, 180nm

- USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm

- USB 2.0 PHY IP, Silicon Proven in UMC 40LP

- USB 2.0 PHY IP, Silicon Proven in UMC 28HPC