You are here:

USB 2.0 EHCI Host Controller IP

The Arasan USB 2.0 Host IP is an USB 2.0 specification compliant host IP core with an optional AHB, PCI, or custom host interface. The USB 2.0 Host IP supports 480 Mbit/s in High Speed (HS) mode. 12 Mbit/s in Full Speed (FS) mode, and 1.5 Mbit/s in Low Speed (LS) mode.

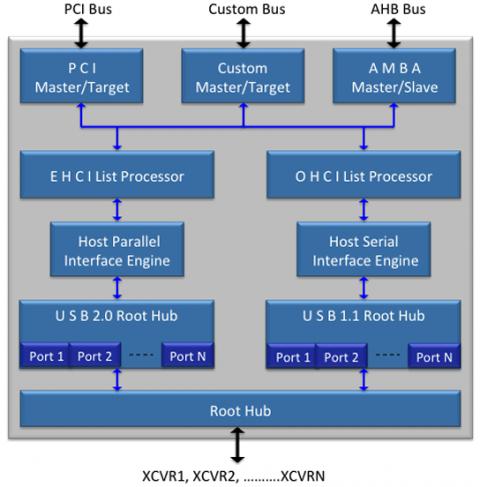

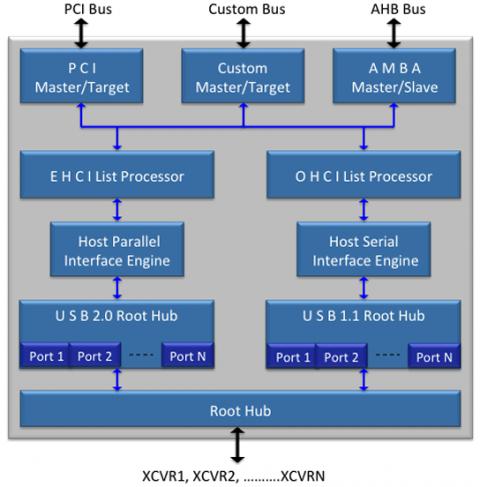

The IP consists of an Enhanced Host Controller Interface (EHCI) and a companion Open Host Controller Interface (OHCI). The EHCI processor handles HS transactions and is the default owner of the root hub that connects to the downstream ports. In a downstream data transfer, the EHCI sends data to the Host Parallel Interface Engine (HPIE) for encoding and CRC appending. Data received by the USB 2.0 Root Hub is forwarded to the downstream ports. Similarly, FS and LS transactions are handled by the OHCI, Host Serial Interface Engine (HSIE), and USB 1.1 Root Hub. The Root Hub performs multiplexing and forwarding of packets between the downstream ports and USB 2.0/1.1 Root Hubs. Up to 8 downstream ports can be connected to the USB 2.0 Host IP core. With the addition of an optional ULPI Wrappers, the Arasan USB 2.0 Host IP core can be connected directly to a 16-bit standard UTMI or 8-bit ULPI transceiver.

The IP consists of an Enhanced Host Controller Interface (EHCI) and a companion Open Host Controller Interface (OHCI). The EHCI processor handles HS transactions and is the default owner of the root hub that connects to the downstream ports. In a downstream data transfer, the EHCI sends data to the Host Parallel Interface Engine (HPIE) for encoding and CRC appending. Data received by the USB 2.0 Root Hub is forwarded to the downstream ports. Similarly, FS and LS transactions are handled by the OHCI, Host Serial Interface Engine (HSIE), and USB 1.1 Root Hub. The Root Hub performs multiplexing and forwarding of packets between the downstream ports and USB 2.0/1.1 Root Hubs. Up to 8 downstream ports can be connected to the USB 2.0 Host IP core. With the addition of an optional ULPI Wrappers, the Arasan USB 2.0 Host IP core can be connected directly to a 16-bit standard UTMI or 8-bit ULPI transceiver.

查看 USB 2.0 EHCI Host Controller IP 详细介绍:

- 查看 USB 2.0 EHCI Host Controller IP 完整数据手册

- 联系 USB 2.0 EHCI Host Controller IP 供应商

Block Diagram of the USB 2.0 EHCI Host Controller IP