You are here:

USB 2.0 Device with FIFO Interface (USB20HF)

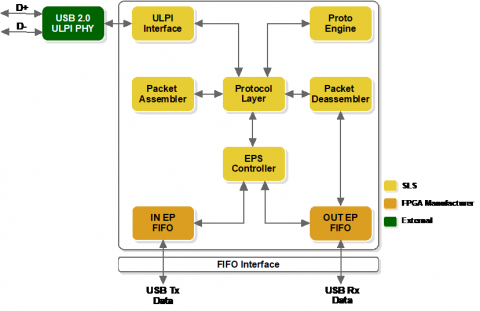

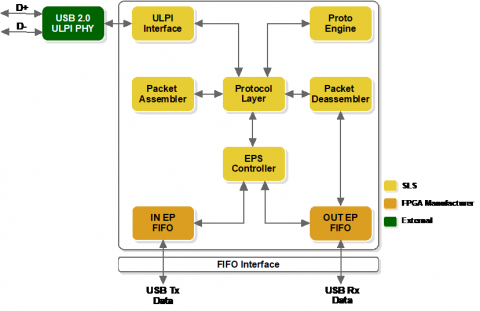

The USB 2.0 Device with FIFO Interface (USB20HF) IP Core supports ULPI interface with Bulk IN and Bulk OUT endpoints. The core supports three preconfigured endpoints Control, Bulk IN, and Bulk OUT. It is Configurable for up to 15 IN/OUT endpoints on customer request on chargeable basis1. Each configurable endpoint has an endpoint controller that supports Interrupt, Bulk, and Isochronous transfers. The USB 2.0 Device IP communicates with the Host through FIFO interface. The core supports both High Speed (480 Mbps) and full Speed (12 Mbps) functionality.

查看 USB 2.0 Device with FIFO Interface (USB20HF) 详细介绍:

- 查看 USB 2.0 Device with FIFO Interface (USB20HF) 完整数据手册

- 联系 USB 2.0 Device with FIFO Interface (USB20HF) 供应商

Block Diagram of the USB 2.0 Device with FIFO Interface (USB20HF)

usb IP

- HDCP 2.3 Embedded Security Modules on DisplayPort/USB Type-C

- USB 2.0 PHY TSMC 5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm, 65nm, 130nm, 180nm

- USB 2.0 PHY GlobalFoundaries 12nm, 22nm, 28nm, 40nm

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- Multi-protocol SerDes PMA in FDSOI (GF22FDX FDX 22FDX) - PCIe1 PCIe2 PCIe3 PCIe4 and more

- Complete USB Type-C Power Delivery PHY, RTL, and Software