USB 2.0 CONTROLLER IP CORE

Options include a protocol aware DMA controller, support for a variety of widely used bus interfaces, and a UTMI Low Pin Interface (ULPI).

Designed for easy reuse in ASIC and FPGA implementations, the microcode-free design is strictly synchronous with positive-edge clocking, no internal tri-states and a synchronous reset; therefore scan insertion is straightforward. The core has been optimized and silicon proven on Xilinx and Altera FPGAs.

查看 USB 2.0 CONTROLLER IP CORE 详细介绍:

- 查看 USB 2.0 CONTROLLER IP CORE 完整数据手册

- 联系 USB 2.0 CONTROLLER IP CORE 供应商

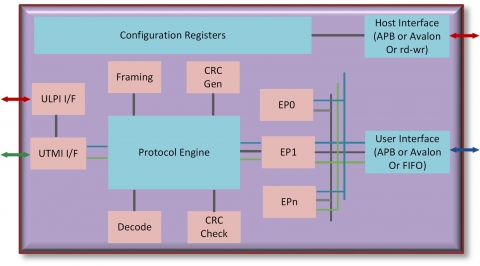

Block Diagram of the USB 2.0 CONTROLLER IP CORE

USB 2.0 Device IP

- USB 2.0 OTG High / Full / Low- Speed Dual Role IP Core

- USB 2.0 PHY IP, Silicon Proven in TSMC 22ULP

- USB 2.0 Device Transceiver PHY

- USB 2.0 Device, Software based enumeration RAM Interface (USB20SR)

- USB 2.0 Device with FIFO Interface (USB20HF)

- USB 2.0 Device, Software Enumeration FIFO Interface (USB20SF)