180nm FTP Non Volatile Memory for Standard CMOS Logic Process

You are here:

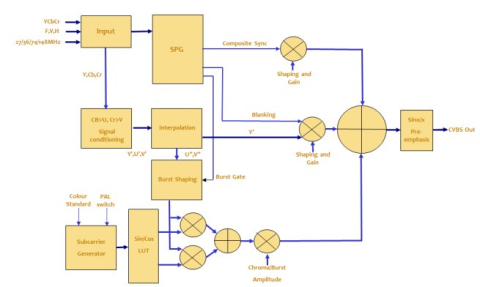

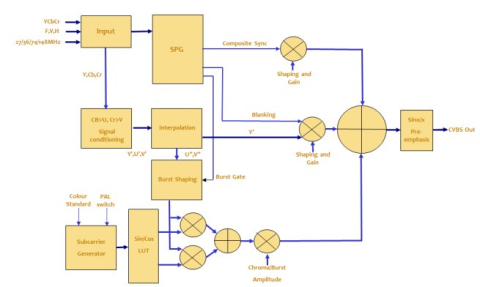

Universal video encoder supporting encoding of NTSC, PAL, 960H, AHD, HD-CVI and HD-TVI

PT57 is a video encoder IP (intellectual property) core supporting NTSC-M/PAL standards as well as 960H NTSC/PAL, and AHD/HD-CVI/HD-TVI analogue HD formats at 720p-25Hz/30Hz, 1080p25Hz/30Hz, 4MP-25Hz/30Hz and 5MP-12.5Hz/20Hz resolutions.

Control and status registers are written to and read from using a conventional 8-bit wide microprocessor interface.

The intellectual property block is provided as RTL compliant Verilog-2001 source code for FPGAs from all vendors or for ASICs.

Control and status registers are written to and read from using a conventional 8-bit wide microprocessor interface.

The intellectual property block is provided as RTL compliant Verilog-2001 source code for FPGAs from all vendors or for ASICs.

查看 Universal video encoder supporting encoding of NTSC, PAL, 960H, AHD, HD-CVI and HD-TVI 详细介绍:

- 查看 Universal video encoder supporting encoding of NTSC, PAL, 960H, AHD, HD-CVI and HD-TVI 完整数据手册

- 联系 Universal video encoder supporting encoding of NTSC, PAL, 960H, AHD, HD-CVI and HD-TVI 供应商

Block Diagram of the Universal video encoder supporting encoding of NTSC, PAL, 960H, AHD, HD-CVI and HD-TVI