You are here:

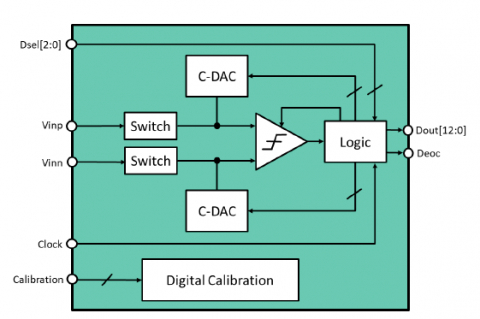

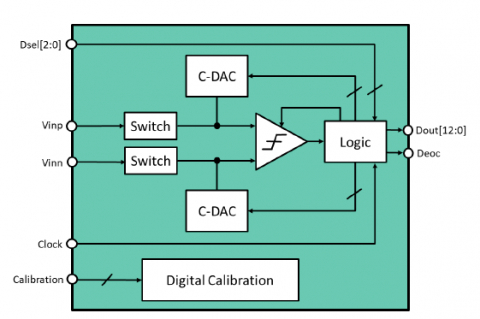

Ultra-Low Power 6 - 13 Bit 1-10 kS/s 1.9 μW SAR ADC

The IP consists of a Successive Approximation Register (SAR) architecture ADC using charge-redistribution technique. The ADC IP is configurable regarding resolution (6-13 bit) and sample rate (up to 10 kS/s) and power consumption down to 1.9 μW. The input voltage range is quasi-ra il -to-ra il guaranteeing more than +-1.7 V@ 1.8 V power supply. An optional calibration technique can be applied to compensate degraded mismatch behavior of technology capacitors.

The ADC IP is applied for industrial and automotive ASIC products.

The ADC IP is silicon evaluated using the XFAB XT018 process. Measurement results and samples are available. The ADC IP was migrated to GF 22FDX and TSMC BCD180 technology with sampling rates up to 2 MS/s.

Fraunhofer IIS/EAS provides a detailed documentation and support for the IP integration. Modifications, extensions and technology ports of the IP are available on request.

The ADC IP is applied for industrial and automotive ASIC products.

The ADC IP is silicon evaluated using the XFAB XT018 process. Measurement results and samples are available. The ADC IP was migrated to GF 22FDX and TSMC BCD180 technology with sampling rates up to 2 MS/s.

Fraunhofer IIS/EAS provides a detailed documentation and support for the IP integration. Modifications, extensions and technology ports of the IP are available on request.

查看 Ultra-Low Power 6 - 13 Bit 1-10 kS/s 1.9 μW SAR ADC 详细介绍:

- 查看 Ultra-Low Power 6 - 13 Bit 1-10 kS/s 1.9 μW SAR ADC 完整数据手册

- 联系 Ultra-Low Power 6 - 13 Bit 1-10 kS/s 1.9 μW SAR ADC 供应商

Block Diagram of the Ultra-Low Power 6 - 13 Bit 1-10 kS/s 1.9 μW SAR ADC