Multi-Video-Source Multiplexing Serial Video Transmitter for MIPI CSI2

You are here:

Ultra-Low Power 6 - 13 Bit 0.5 -10 kS/s 10μW Analog Front End

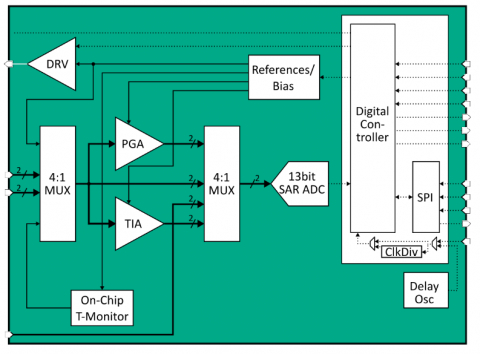

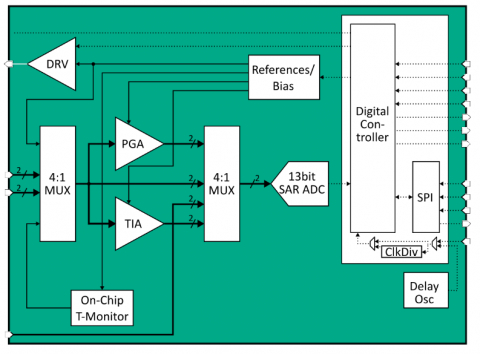

The Analog-Frontend (AFE) IP consists of programmable current and voltage preamplifier followed by a Successive Approximation Register (SAR) architecture ADC using charge-redistribution technique. The ADC IP is configurable regarding resolution (6-13 bit) and sample rate (up to 10kS/s). The preamplifier offers programmable gain from 0.5 to 4. The input voltage range is quasi-rail-to-rail guaranteeing more than +- 1.7 V @ 1.8 V power supply. An optional calibration technique can be applied to compensate degraded mismatch behavior of t echnology capacitors. The overall power consumption of the AFE IP sums up with 10.5 μW at 1 kHz input signal.

The AFE ASIC with current and voltage input channels was applied to commercial environmental sensors for ambient light, temperature and CO gas. An internal temperature monitor is included.

The AFE ASIC as well as the stand-alone SAR ADC are silicon evaluated using the XFAB XT018 process. Measurement results and samples are available.

The AFE IP was migrated to GF 22FDX. Fraunhofer IIS/EAS provides a detailed documentation and support for the IP integration. Modifications, extensions and technology ports of the IP are available on request.

The AFE ASIC with current and voltage input channels was applied to commercial environmental sensors for ambient light, temperature and CO gas. An internal temperature monitor is included.

The AFE ASIC as well as the stand-alone SAR ADC are silicon evaluated using the XFAB XT018 process. Measurement results and samples are available.

The AFE IP was migrated to GF 22FDX. Fraunhofer IIS/EAS provides a detailed documentation and support for the IP integration. Modifications, extensions and technology ports of the IP are available on request.

查看 Ultra-Low Power 6 - 13 Bit 0.5 -10 kS/s 10μW Analog Front End 详细介绍:

- 查看 Ultra-Low Power 6 - 13 Bit 0.5 -10 kS/s 10μW Analog Front End 完整数据手册

- 联系 Ultra-Low Power 6 - 13 Bit 0.5 -10 kS/s 10μW Analog Front End 供应商

Block Diagram of the Ultra-Low Power 6 - 13 Bit 0.5 -10 kS/s 10μW Analog Front End

Ultra-Low Power IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-100 ultra-low power 32-bit RISC-V processor for embedded applications

- GNSS (GPS, Galileo, GLONASS, Beidou3, QZSS, SBAS) Ultra-low power RF Receiver IP

- Ultra-low power 32 kHz RC oscillator designed in GlobalFoundries 22FDX

- 8-Channel Ultra-Low Power Capacitive Touch Interface

- Compact ARC EM Processors feature excellent code density, small size, and ultra-low power consumption for power-sensitive, area-critical embedded applications