You are here:

Ultra-Low-Latency 10GE PHY+MAC

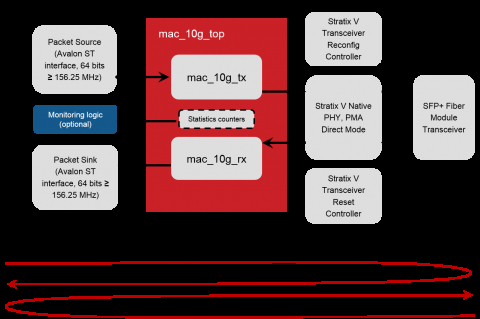

Having the lowest network latency is critical for Accelerated Finance. To achieve the lowest Ethernet latency, it is necessary to optimize the layer-1 PHY and the layer-2 MAC. Algo-Logic Systems’ Ultra-Low-Latency (ULL) PHY+MAC minimizes roundtrip latency by several hundred nanoseconds as compared to vendor supplied IP cores. Algo-Logic Systems’ ULL PHY+MAC design implements 10GBASE-R MAC and PCS (Physical Coding Sub-layer) functionality in an FPGA by using logic optimized for latency.

The ULL PHY+MAC is compatible with multiple FPGA platforms that support SERDES rates of 10.3125 Gbps while bypassing all PCS and excessive buffering features. The MAC interfaces to user logic via the 64-bit Avalon-ST bus or AXI4-Stream standards.

In this fashion, Algo-Logic Systems’ ULL PHY+MAC is designed to seamlessly replace much slower default PHY+MAC implementations that come with standard FPGA platforms.

The ULL PHY+MAC is compatible with multiple FPGA platforms that support SERDES rates of 10.3125 Gbps while bypassing all PCS and excessive buffering features. The MAC interfaces to user logic via the 64-bit Avalon-ST bus or AXI4-Stream standards.

In this fashion, Algo-Logic Systems’ ULL PHY+MAC is designed to seamlessly replace much slower default PHY+MAC implementations that come with standard FPGA platforms.

查看 Ultra-Low-Latency 10GE PHY+MAC 详细介绍:

- 查看 Ultra-Low-Latency 10GE PHY+MAC 完整数据手册

- 联系 Ultra-Low-Latency 10GE PHY+MAC 供应商

Block Diagram of the Ultra-Low-Latency 10GE PHY+MAC