LDO Voltage Regulator, 30 mA, Adjustable 0.45 V to 0.9 V Output

You are here:

Ultra-low jitter, type-I ADDLL with adaptive dither cancellation-3GHz-5GHz

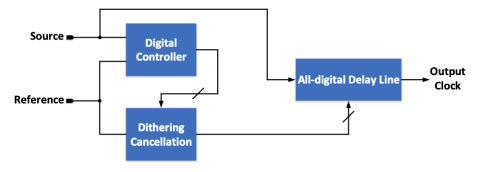

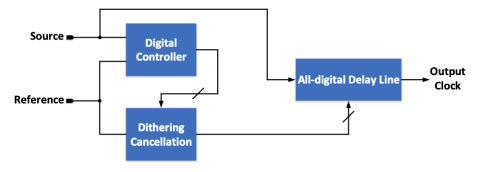

InCirT’s Type-I ADDLL5GGF22 is an all-digital delay-locked loop (ADDLL) featuring an adaptive dithering cancellation technique. This innovation ensures ultra-low jitter performance (less than 1 ps RMS jitter at 5 GHz) while maintaining low power consumption (15mW at 5 GHz) and operating within a frequency range of 3 GHz to 5 GHz. The ADDLL5GGF22 aligns its high-speed source clock with a reference clock operating at up to 1 GHz.

With an ultra-compact footprint (0.008 sq mm), it is particularly suited for SoC designs that require precise phase synchronization across multiple clock domains. The delay resolution is as fine as 700 fs. Thanks to its adaptive dithering cancellation technique, it mitigates dithering issues, significantly enhancing jitter performance.

With an ultra-compact footprint (0.008 sq mm), it is particularly suited for SoC designs that require precise phase synchronization across multiple clock domains. The delay resolution is as fine as 700 fs. Thanks to its adaptive dithering cancellation technique, it mitigates dithering issues, significantly enhancing jitter performance.

查看 Ultra-low jitter, type-I ADDLL with adaptive dither cancellation-3GHz-5GHz 详细介绍:

- 查看 Ultra-low jitter, type-I ADDLL with adaptive dither cancellation-3GHz-5GHz 完整数据手册

- 联系 Ultra-low jitter, type-I ADDLL with adaptive dither cancellation-3GHz-5GHz 供应商

Block Diagram of the Ultra-low jitter, type-I ADDLL with adaptive dither cancellation-3GHz-5GHz

Low jitter IP

- TSMC GF Intel Low Phase Noise, High-performance Digital LC PLL

- Low jitter 4.96GHz to 5.6GHz PLL in TSMC N40

- PCIe/HCSL Differential IO Buffer - TSMC 16FFC

- Low jitter, low-power clock-deskew PLL operating from 6GHz to 9.5GHz

- Low jitter, ultra-low power (<950uW) ring-oscillator-based PLL-2.4GHz

- 25MHz Low Jitter Low Power XTAL Oscillator with AGC