LDO Voltage Regulator, 30 mA, Adjustable 0.45 V to 0.9 V Output

You are here:

Ultra Compact 32-bit RISC-V CPU Core

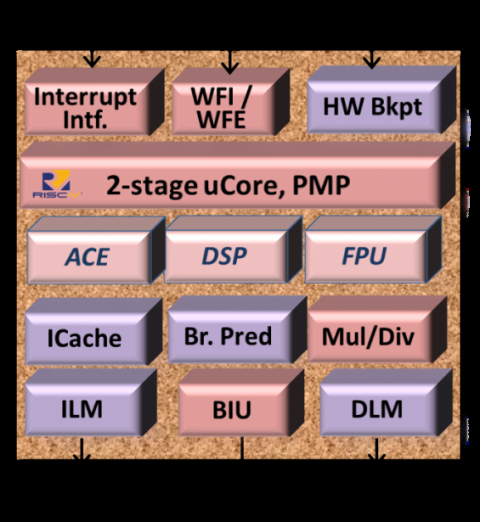

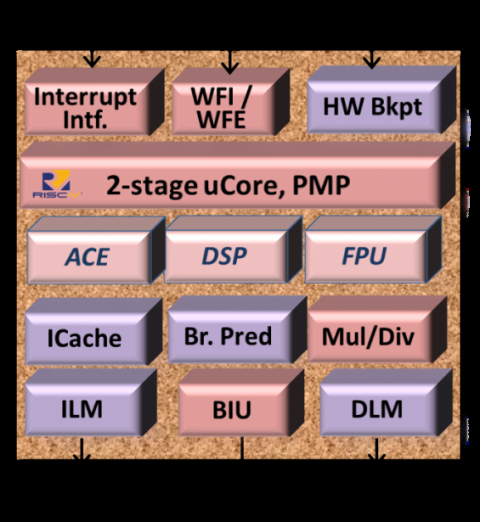

AndesCore™ N22 is a 32-bit 2-stage pipeline CPU IP core based on AndeStar™ V5 architecture for embedded applications that require low energy consumption and small area. It is compliant to RISC-V technology with several efficient performance features, including simple dynamic branch prediction, instruction cache, and local memories. It supports 32 or 16 general purpose registers (GPRs) and fast or small multiplier for performance/area tradeoff. In addition, it comes with rich optional features to ease SoC integration such as vectored CLIC and PLIC for design flexibility, AHB-Lite 32-bit bus for system integration, Fast I/O interface for low latency accesses, APB for CPU local peripherals, PowerBrake and WFI/WFE mode for low power and power management, and JTAG debug interface for development support.

查看 Ultra Compact 32-bit RISC-V CPU Core 详细介绍:

- 查看 Ultra Compact 32-bit RISC-V CPU Core 完整数据手册

- 联系 Ultra Compact 32-bit RISC-V CPU Core 供应商

Block Diagram of the Ultra Compact 32-bit RISC-V CPU Core