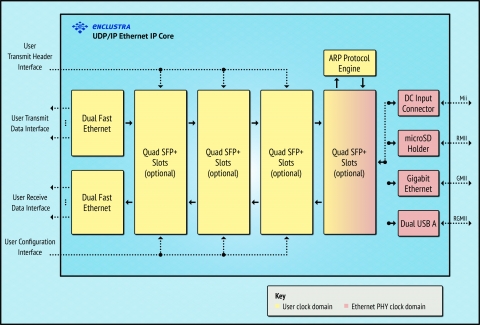

Enclustra's UDP/IP Ethernet IP core easily enables FPGA-based subsystems to communicate with other subsystems via Ethernet, using the UDP protocol. The IP core is highly configurable and optimally implemented for the use in current Altera® and Xilinx® FPGA architectures. It provides a simple to use interface to the user logic, and supports the common media independent interfaces MII, RMII, GMII and RGMII. With its 8-bit wide transmit and receive interfaces running at 125 MHz, the IP core is able to operate at full 1 Gbit/sec wire speed. 100 Mbit/sec and 10 Mbit/sec operation is also supported.