25kHz 1.71-5.5V Oscillator Low Power, ± 1% accuracy at @ 27◦C after trimming

You are here:

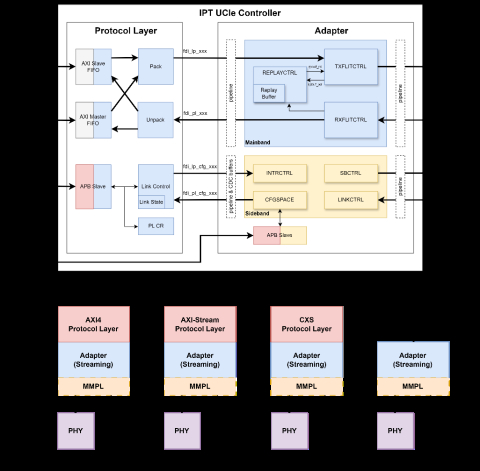

UCIE 2.0 Controller

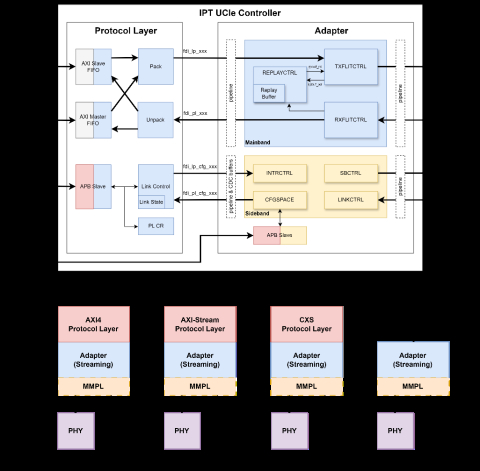

The InPsytech UCIe 2.0 (Universal Chiplet Interconnect Express) Controller is a high-performance designe to facilitate efficient communication between Die-to-Die or Chip-to-Chip for AI server, data centers, and consumer electronics application. The controller IP enables seamless integration and data exchange across multiple chiplet architecture, supporting complete streaming protocol formats (1–6). Its robust controller design ensures high bandwidth and low latency, making it ideal for applications demanding quick and reliable data transmission.

The controller IP supports multiple BUS fabrics, including AXI4, AXI-Stream, CXS and Adapter direct access (for latency sensitive application), offering flexibility in connecting various components within the SoC. It also provides power optimization features such as dynamic clock gating and Power Management (PM) states (L1/L2) to reduce energy consumption without compromising performance. With flexible configuration options, including lane degradation and multi-module configurations, the UCIe controller can be adapted to meet diverse system requirements while ensuring high reliability, low Bit Error Rate (BER), and transmission integrity.

The controller IP supports multiple BUS fabrics, including AXI4, AXI-Stream, CXS and Adapter direct access (for latency sensitive application), offering flexibility in connecting various components within the SoC. It also provides power optimization features such as dynamic clock gating and Power Management (PM) states (L1/L2) to reduce energy consumption without compromising performance. With flexible configuration options, including lane degradation and multi-module configurations, the UCIe controller can be adapted to meet diverse system requirements while ensuring high reliability, low Bit Error Rate (BER), and transmission integrity.

查看 UCIE 2.0 Controller 详细介绍:

- 查看 UCIE 2.0 Controller 完整数据手册

- 联系 UCIE 2.0 Controller 供应商

Block Diagram of the UCIE 2.0 Controller