PCIe 4.0 Controller supporting Endpoint, Root Port, Switch, Bridge and advanced features

三倍速以太网MAC

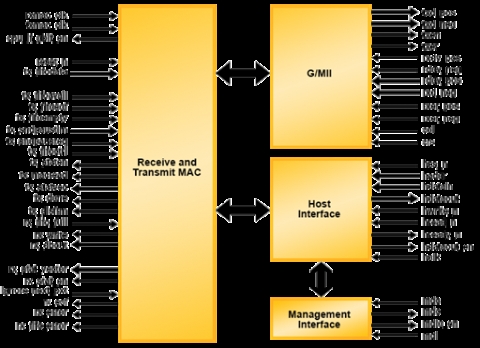

三倍速以太网路媒体接入控制器发送和接收主机处理器和一个以太网网络之间的数据。以太网MAC的主要功能是要确保媒体接入满足802.3 IEEE标准指定的规则的同时,通过以太网传输数据帧。关于接收方面,以太网MAC提取帧的不同组成部分,并通过FIFO接口将他们传输到更高层的应用。

从G/MII接口所收到的数据,首先进行缓冲,直到接收MAC ( Rx MAC )有足够的数据可供处理 。然后从输入帧中提取前导和帧定界符(SFD)开始的信息,以确定一个有效帧的开始。接收MAC检查收到的信息包的地址,并验证是否可以在发送到FIFO之前接收到帧。只有有效帧才被传输到FIFO中 。此功能有以下两个好处:当帧正在传送时,该系统无须重新计算帧校验序列( FCS ),而且还保持接受MAC相对简单。然而,三倍速以太网路媒体接入控制器总是计算CRC,以检查收到的帧是否无差错。

在传输方面,Tx MAC 负责控制对物理介质的访问。 德克萨斯州 MAC 将数据从外部客户端 Tx FIFO,格式此数据读入一个以太网数据包,然后将它传递给 G/信产部模块。 德克萨斯州 MAC 读取来自德克萨斯州客户端 FIFO 时,客户端指示数据包的数据是可用的和 Tx MAC 是在它适当的状态。 德克萨斯州 MAC 预修复序言和对数据的起始帧分隔符信息,并将追加帧检查序列末尾的数据。 在半双工操作,Tx MAC 存储来自外部的 FIFO 在内部缓冲区中,在重新传送数据的碰撞中使用的数据的第一个 64 字节。 SGMII 轻松连接的配置选项将针脚和无缝连接的逻辑添加到格子的千兆位以太网 PC IP 核心。

查看 三倍速以太网MAC 详细介绍:

- 查看 三倍速以太网MAC 完整数据手册

- 联系 三倍速以太网MAC 供应商

Block Diagram of the 三倍速以太网MAC

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software