You are here:

Tiny UART

The DUART is one of the tiniest UART IP Cores available on the market.

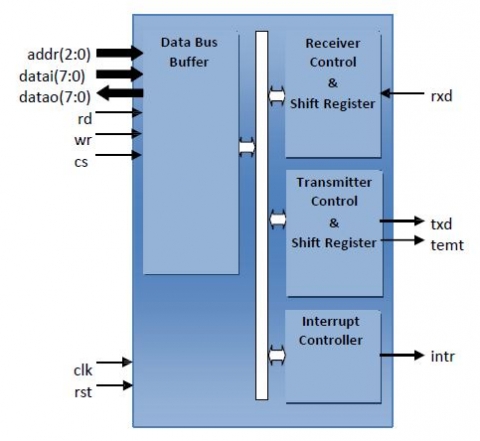

The DUART is a soft core of a Universal Asynchronous Receiver/Transmitter (UART). It performs serial-to-parallel conversion on data characters received from a peripheral device or a MODEM, and parallel-to-serial conversion on data characters received from the CPU. The CPU can read the complete status of the UART at any time during the functional operation. Status information reported includes the type and condition of the transfer operations being performed by the UART, as well as any error conditions (overrun, framing). The DμART includes a programmable baud rate generator that is capable of dividing the timing reference clock input by divisors of 1 to (216-1), and producing a 16 × clock for driving the internal transmitter logic. Provisions are also included to use this 16 × clock to drive the receiver logic. The DμART has processor-interrupt system. Interrupts can be programmed to the user’s requirements, minimizing the computing required to handle the communications link.

The core is perfect for applications, where the UART Core and microcontroller are clocked by the same clock signal and are implemented inside the same ASIC or FPGA chip, as well as for standalone implementation, where several UARTs are required to be implemented inside a single chip, and driven by some off-chip devices.

The DUART is a soft core of a Universal Asynchronous Receiver/Transmitter (UART). It performs serial-to-parallel conversion on data characters received from a peripheral device or a MODEM, and parallel-to-serial conversion on data characters received from the CPU. The CPU can read the complete status of the UART at any time during the functional operation. Status information reported includes the type and condition of the transfer operations being performed by the UART, as well as any error conditions (overrun, framing). The DμART includes a programmable baud rate generator that is capable of dividing the timing reference clock input by divisors of 1 to (216-1), and producing a 16 × clock for driving the internal transmitter logic. Provisions are also included to use this 16 × clock to drive the receiver logic. The DμART has processor-interrupt system. Interrupts can be programmed to the user’s requirements, minimizing the computing required to handle the communications link.

The core is perfect for applications, where the UART Core and microcontroller are clocked by the same clock signal and are implemented inside the same ASIC or FPGA chip, as well as for standalone implementation, where several UARTs are required to be implemented inside a single chip, and driven by some off-chip devices.

查看 Tiny UART 详细介绍:

- 查看 Tiny UART 完整数据手册

- 联系 Tiny UART 供应商