syn1588® enabled IEEE 1588 compliant clock synchronisation

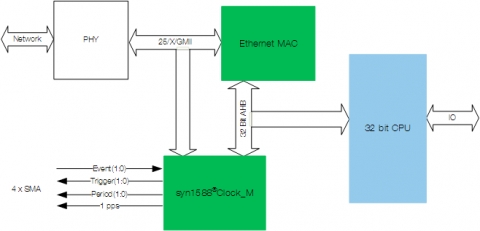

A typical application example is the syn1588® PCIe NIC. A standard PCIe Ethernet network interface card is made up of a single FPGA that includes the syn1588® Clock_M IP core as well as the Ethernet MAC and the PCIe interface

查看 syn1588® enabled IEEE 1588 compliant clock synchronisation 详细介绍:

- 查看 syn1588® enabled IEEE 1588 compliant clock synchronisation 完整数据手册

- 联系 syn1588® enabled IEEE 1588 compliant clock synchronisation 供应商

Block Diagram of the syn1588® enabled IEEE 1588 compliant clock synchronisation