You are here:

Stream Buffer Controller

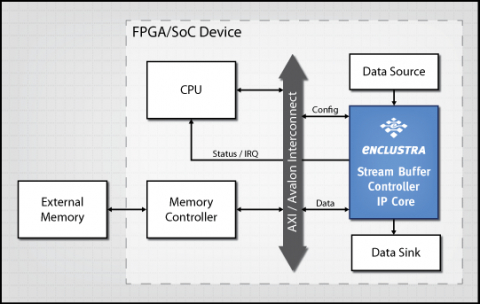

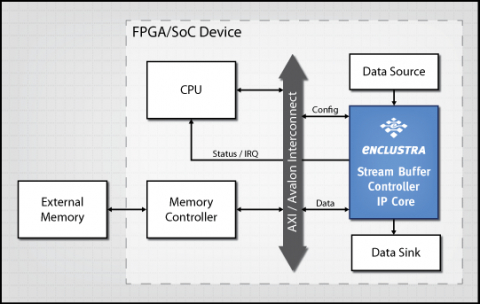

The Stream Buffer Controller IP Core is optimized for Intel (Altera) and Xilinx FPGAs and implements a versatile Stream to Memory Mapped DMA bridge with 16 independent streams. The IP core allows data buffering in an external memory device to provide virtual FIFO capability with up to 4 GB memory size. It provides AMBA® AXI4-Stream interfaces for each write and read data stream. A common memory-mapped master interface (AXI or Avalon) is provided to access the external memory device over an interconnect.

The IP core is highly configurable in terms of operation mode, buffer size and buffer address for each stream. The configuration is done over a memory mapped slave interface, either by an embedded-CPU, by a FPGA Manager application or by an application specific stream configurator controller in VHDL.

The IP core is highly configurable in terms of operation mode, buffer size and buffer address for each stream. The configuration is done over a memory mapped slave interface, either by an embedded-CPU, by a FPGA Manager application or by an application specific stream configurator controller in VHDL.

查看 Stream Buffer Controller 详细介绍:

- 查看 Stream Buffer Controller 完整数据手册

- 联系 Stream Buffer Controller 供应商

Block Diagram of the Stream Buffer Controller

Stream Buffer Controller IP

- Stream Buffer Controller

- Compute Express Link (CXL) 2.0 Controller with AMBA AXI interface

- PCIe 5.0 Controller supporting Endpoint, Root Port, Switch, Bridge and advanced features

- PCIe 5.0 Controller with AMBA AXI interface

- PCIe 4.0 Controller with AMBA AXI interface

- MIPI CSI-2 TX Controller for v2.1