You are here:

Standard SPI Single Master

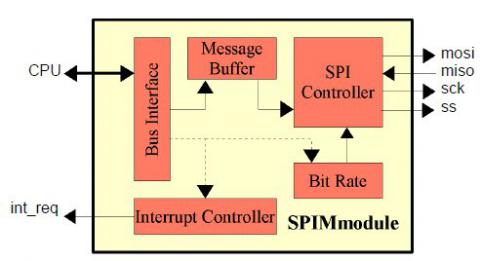

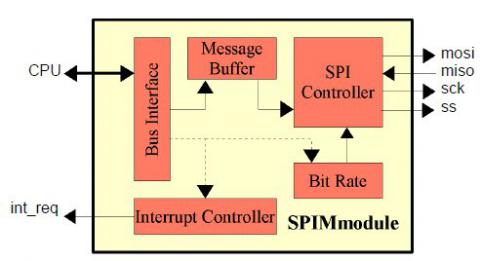

The Standard SPI Single Master is a single master controller and uses a message queue based architecture. A message consists of the command, transmit data and receive data field. The command field defines the length of the SPI access (1-32 bits, or

continued in the next command), the selected slave device, the SS to SCK delay and the delay after transfer control. Using the queue, several SPI commands can be executed without CPU interaction.

A range of messages can be selected to be sent by the SPI controller. There is a wrap mode to enable continuously sending the same messages.

The SPI controller supports all standard modes. The clock phase and clock polarity can be configured as well as the bit rate and slave select polarity.

The serial peripheral interface (SPI) protocol is often used to connect peripheral devices to a CPU. Several slave devices can be connected to the same bus. Since it is a serial bus, the pin count is low.

continued in the next command), the selected slave device, the SS to SCK delay and the delay after transfer control. Using the queue, several SPI commands can be executed without CPU interaction.

A range of messages can be selected to be sent by the SPI controller. There is a wrap mode to enable continuously sending the same messages.

The SPI controller supports all standard modes. The clock phase and clock polarity can be configured as well as the bit rate and slave select polarity.

The serial peripheral interface (SPI) protocol is often used to connect peripheral devices to a CPU. Several slave devices can be connected to the same bus. Since it is a serial bus, the pin count is low.

查看 Standard SPI Single Master 详细介绍:

- 查看 Standard SPI Single Master 完整数据手册

- 联系 Standard SPI Single Master 供应商

Block Diagram of the Standard SPI Single Master

SPI Single Master IP

- Serial Peripheral Interface - Master/Slave with single, dual, quad and octal SPI Bus support

- Serial Peripheral Interface - Master/Slave with single, dual and quad SPI Bus support

- Serial Peripheral Interface – Master/Slave with Octal, Quad, Dual and Single SPI Bus support

- SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL and QUAD SPI Bus Controller with DDR / DTR support and optional AES Encryption)

- Enhanced Serial Peripheral Interface – Master/Slave with single, dual, and quad eSPI Bus support for Intel CPU’s

- QSPI FLASH Controller – XIP functionality (SINGLE, DUAL and QUAD SPI Bus Controller with Double Data Rate support)