You are here:

SNOW-V Stream Cipher Engine

The SNOW-V IP core implements the SNOW-V stream cipher mechanism, aiming to meet the security demands of modern high-speed communication systems. It conforms to the official SNOW-V mechanism, published in 2019 by the IACR Transactions on Symmetric Cryptology, as an extensive revision of SNOW 3G stream cipher.

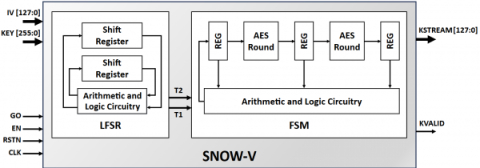

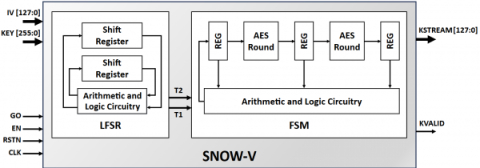

Receiving a 256-bit Key and a 128-bit Initialization Vector (IV), the core processes 128 bits of information in one cycle and it produces a stream of 128-bit keys. It employs two main building blocks, a Linear Feedback Shift Register (LFSR) and a Finite State Machine (FSM) that applies an Advanced Encryption Standard (AES) round function.

The core can be easily incorporated in a Galois/Counter mode (GCM) topology and by interoperating with a Galois Message Authentication Code (GMAC) realize an Authenticated Encryption with Associated Data (AEAD) mechanism. What is more, the core is a drop-in replacement for SNOW 3G in EPS Encryption/Integrity Algorithm (EEA/EIA) architectures and New Radio Encryption/Integrity Algorithm (NEA/NIA) architectures for 4G and 5G communications, while also targeting future mobile network generations (e.g. 6G).

The SNOW-V IP core is a microcode-free and fully synchronous design developed for reuse in ASIC and FPGA implementations, aiming at throughput-demanding environments. The efficient and compact hardware design enables notably high throughput, achieving over 100 Gbps in mainstream ASIC technologies and over 40 Gbps in high-end AMD and Altera FPGAs. Moreover, being a scan-ready, LINT-clean, and single-clock design with a simple handshake interface, facilitates straightforward integration

Receiving a 256-bit Key and a 128-bit Initialization Vector (IV), the core processes 128 bits of information in one cycle and it produces a stream of 128-bit keys. It employs two main building blocks, a Linear Feedback Shift Register (LFSR) and a Finite State Machine (FSM) that applies an Advanced Encryption Standard (AES) round function.

The core can be easily incorporated in a Galois/Counter mode (GCM) topology and by interoperating with a Galois Message Authentication Code (GMAC) realize an Authenticated Encryption with Associated Data (AEAD) mechanism. What is more, the core is a drop-in replacement for SNOW 3G in EPS Encryption/Integrity Algorithm (EEA/EIA) architectures and New Radio Encryption/Integrity Algorithm (NEA/NIA) architectures for 4G and 5G communications, while also targeting future mobile network generations (e.g. 6G).

The SNOW-V IP core is a microcode-free and fully synchronous design developed for reuse in ASIC and FPGA implementations, aiming at throughput-demanding environments. The efficient and compact hardware design enables notably high throughput, achieving over 100 Gbps in mainstream ASIC technologies and over 40 Gbps in high-end AMD and Altera FPGAs. Moreover, being a scan-ready, LINT-clean, and single-clock design with a simple handshake interface, facilitates straightforward integration

查看 SNOW-V Stream Cipher Engine 详细介绍:

- 查看 SNOW-V Stream Cipher Engine 完整数据手册

- 联系 SNOW-V Stream Cipher Engine 供应商

Block Diagram of the SNOW-V Stream Cipher Engine

SNOW-V Stream Cipher Engine IP

- ICE-IP-338 High-speed XTS-GCM Multi Stream Inline Cipher Engine

- ICE-IP-358 High-speed XTS-GCM Multi Stream Inline Cipher Engine, DPA resistant

- Multi-Protocol Crypto Engine with Classification

- Secure-IC's Securyzr™ ChaCha20-Poly1305 Crypto Engine

- MACsec Protocol Engine for 10/100/1000 Ethernet

- ZUC Crypto Engine