You are here:

Single, Dual and Quad SPI Flash Controller with Boot and Execute On-The-Fly Features

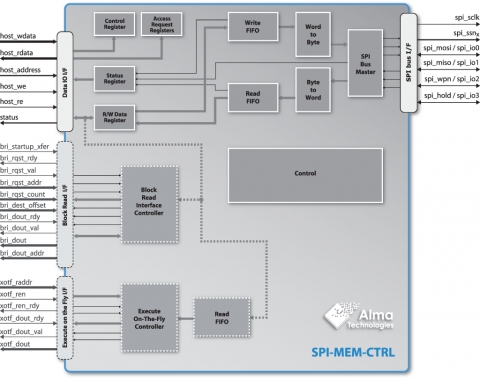

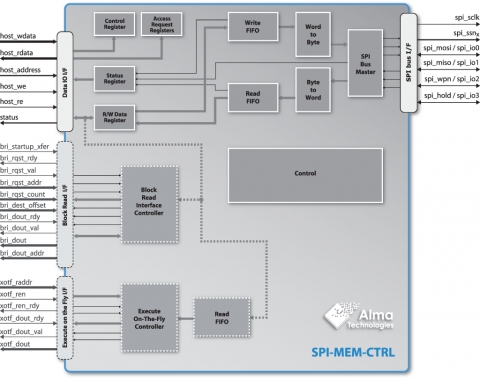

The SPI-MEM-CTRL core from Alma Technologies offers the interconnection between a host and an SPI Flash memory device. The SPI-MEM-CTRL supports Single, Dual Input, Dual Input/Output, Quad Output and Quad Input/Output SPI protocol accesses and optionally includes Boot and Execute On-The-Fly support.

The core automatically identifies a variety of serial flash memories and communicates with the attached device at the maximum possible bandwidth. Register accesses are used to insert access requests and read/write data into/out SPI-MEM-CTRL core. Communication with devices other than those automatically identified, is also feasible as the core can be programmed with the memory device parameters. The SPI-MEM-CTRL can read, write or erase any part of the memory.

The core is rigorously verified. A complete verification environment that helps designers verify the functionality and compliance of the core, and additional aids for system-level simulation are available.

The core automatically identifies a variety of serial flash memories and communicates with the attached device at the maximum possible bandwidth. Register accesses are used to insert access requests and read/write data into/out SPI-MEM-CTRL core. Communication with devices other than those automatically identified, is also feasible as the core can be programmed with the memory device parameters. The SPI-MEM-CTRL can read, write or erase any part of the memory.

The core is rigorously verified. A complete verification environment that helps designers verify the functionality and compliance of the core, and additional aids for system-level simulation are available.

查看 Single, Dual and Quad SPI Flash Controller with Boot and Execute On-The-Fly Features 详细介绍:

- 查看 Single, Dual and Quad SPI Flash Controller with Boot and Execute On-The-Fly Features 完整数据手册

- 联系 Single, Dual and Quad SPI Flash Controller with Boot and Execute On-The-Fly Features 供应商

Block Diagram of the Single, Dual and Quad SPI Flash Controller with Boot and Execute On-The-Fly Features

SPI Flash Controller IP

- Flash SPI controller master/slave

- xSPI NOR Flash controller

- SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL and QUAD SPI Bus Controller with DDR / DTR support and optional AES Encryption)

- Slave side SPI/QPI controller 133MHZ

- Quad-SPI FLASH Controller AHB

- Controller IP, SPI Flash controller, Soft IP