串行RapidIO 2.1端点IP核

使用AMC评估平台对SRIO 2.1 IP核进行评估 LatticeECP3 AMC演示套件包括:

* LatticeECP3 AMC评估板

* 连接电缆

* AMC接口卡

* 演示位流和文件

查看 串行RapidIO 2.1端点IP核 详细介绍:

- 查看 串行RapidIO 2.1端点IP核 完整数据手册

- 联系 串行RapidIO 2.1端点IP核 供应商

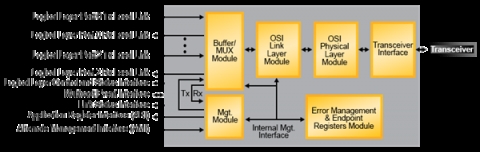

Block Diagram of the 串行RapidIO 2.1端点IP核

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software