You are here:

Serial Peripheral Interconnect Master & Slave Interface Controller

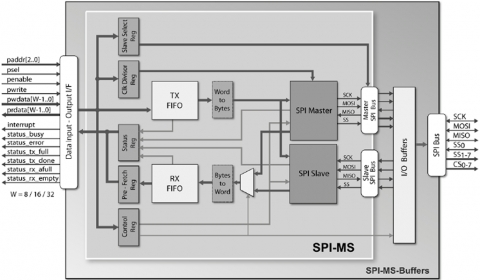

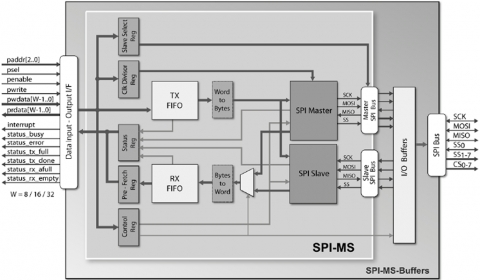

The SPI-MS core from Alma Technologies implements a Serial Peripheral Interconnect interface controller, which can operate either as a Master or a Slave. The Serial Peripheral Interface (SPI) allows high-speed synchronous serial data transfer between microprocessors / microcontrollers and peripheral devices.

When operating in master mode, the core generates the Serial data Clock (SCK) and selects the slave device which will be accessed. When operating in Slave mode, another master device generates the SCK and activates the slave select input of the core to signal communication.

The SPI Slave was carefully designed to provide the most reliable communication possible. The design is fully synchronous and has one clock domain, the system clock. No special technology features are used, so the RTL source code can be easily transferred to any technology. Other features incorporated in the core are the support for 8 Slave Select lines used to access up to 8 devices when working as a master. The ability to program the transfer order of the bits, MSB first or LSB first, is also implemented.

When operating in master mode, the core generates the Serial data Clock (SCK) and selects the slave device which will be accessed. When operating in Slave mode, another master device generates the SCK and activates the slave select input of the core to signal communication.

The SPI Slave was carefully designed to provide the most reliable communication possible. The design is fully synchronous and has one clock domain, the system clock. No special technology features are used, so the RTL source code can be easily transferred to any technology. Other features incorporated in the core are the support for 8 Slave Select lines used to access up to 8 devices when working as a master. The ability to program the transfer order of the bits, MSB first or LSB first, is also implemented.

查看 Serial Peripheral Interconnect Master & Slave Interface Controller 详细介绍:

- 查看 Serial Peripheral Interconnect Master & Slave Interface Controller 完整数据手册

- 联系 Serial Peripheral Interconnect Master & Slave Interface Controller 供应商

Block Diagram of the Serial Peripheral Interconnect Master & Slave Interface Controller