Serial FPDP

StreamDSP is committed to performance, efficiency, and flexibility. Our sFPDP core is unique in that we support nearly all transceiver based devices from Altera and Xilinx. We’re always making improvements to the core with innovative new features such as multi-lane bonding for increased bandwidth, and we’re continually updating the core to support new transceiver based devices offered by both Altera and Xilinx. Our core provides a open interface to the FPGA transceiver, giving the user complete control over transceiver speed, settings and adjustments. A complete reference design is provided for each family, as well as a thorough testbench with support for Aldec's Active- HDL and Riviera-Pro as well as Mentor's ModelSim tools. In addition, our testing procedure includes exhaustive Altera <-> Xilinx interoperability testing to ensure compatibility.

StreamDSP is committed to delivering the highest level of customer support to ensure a smooth system integration. We also offer IP core customization and FPGA design services.

查看 Serial FPDP 详细介绍:

- 查看 Serial FPDP 完整数据手册

- 联系 Serial FPDP 供应商

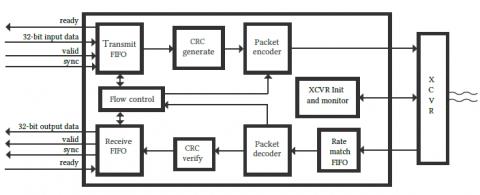

Block Diagram of the Serial FPDP