You are here:

RSA IP Core

RSA IP Cores perform digital signature generation and verification in compliance with the RSA (Rivest-Shamir-Adleman) Digital Signature Algorithm specifications defined in 'FIPS 186'. This standard specifies methods for digital signature generation and verification using the RSA Digital Signature Algorithm. RSA IP cores support bit lengths from 256 to 4096.

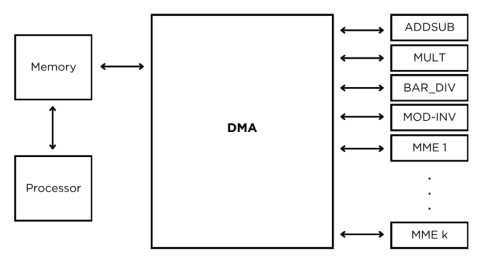

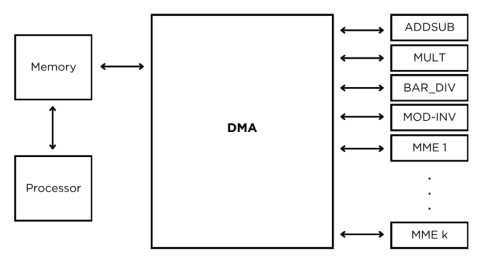

RSA IP cores consist of a cluster of IPs. VHDL is used as the Hardware Description Language of the IP Cores. The cluster includes ADDSUB (Addition and substruction), MULT (Multiplication), BAR_DIV (Barrett Divider), MOD_INV (Modulo Inversion) and MME (Montgomery Modulo Exponentiation) IP Cores. MME cores are configurable, and their number can be changed.

RSA IP cores consist of a cluster of IPs. VHDL is used as the Hardware Description Language of the IP Cores. The cluster includes ADDSUB (Addition and substruction), MULT (Multiplication), BAR_DIV (Barrett Divider), MOD_INV (Modulo Inversion) and MME (Montgomery Modulo Exponentiation) IP Cores. MME cores are configurable, and their number can be changed.

查看 RSA IP Core 详细介绍:

- 查看 RSA IP Core 完整数据手册

- 联系 RSA IP Core 供应商

Block Diagram of the RSA IP Core

RSA IP

- Secure-IC Securyzr™ Tunable Cryptography solutions with embedded side-channel protections: AES - SHA2 - SHA3 - PKC - RSA - ECC - ML-KEM - ML-DSA - XMSS - LMS - SM2 - SM3 - SM4 - Whirlpool - CHACHA20 - Poly1305

- Secure-IC's Securyzr™ Tunable Public Key Cryptographic (RSA, ECDSA, SM2, Diffie-Hellman) accelerator - optional SCA protection

- RSA Keygen IP Core

- Java Card compliant cryptographic library for encryption and decryption of RSA, DSA, Diffie-Hellman, El-Gamal and Elliptic Curves algorithms

- Hardware accelerator for RSA, DSA, Diffie-Hellman, El-Gamal and Elliptic Curves algorithms

- Secure cryptographic library compliant with the X9.31 and FIPS 186-4 standards.