You are here:

RISC-V CPU IP With ISO 26262 Full Compliance

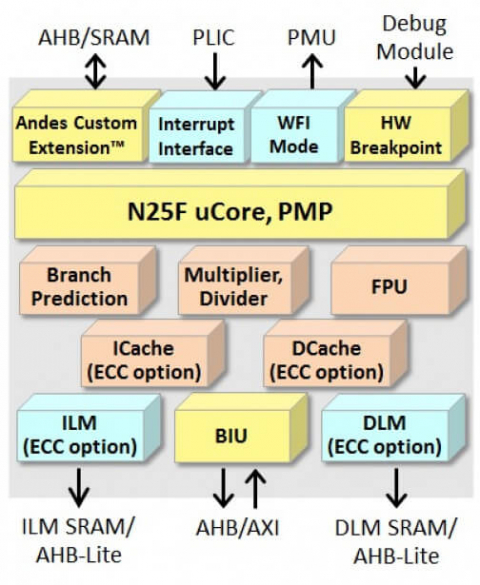

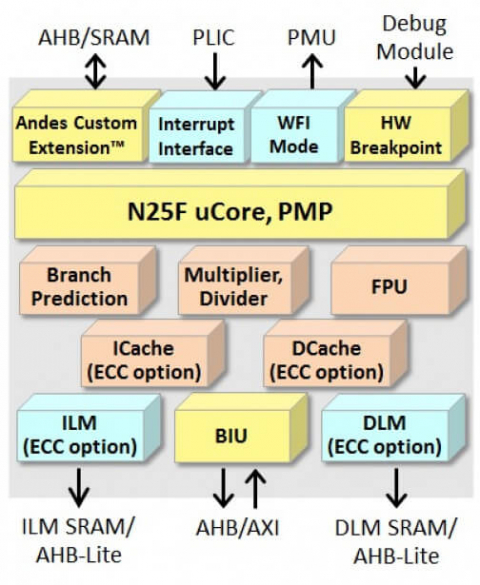

AndesCore™ N25F is a 32-bit CPU IP core based on AndeStar™ V5 architecture which incorporated RISC-V technology, it is capable of delivering high per-MHz performance and operating at high frequencies, at the same time it is small in gate count. N25F also supports single- and double-precision floating point and bit-manipulation instructions. N25F comes with options, including branch prediction for efficient branch execution, Instruction and Data caches, Local Memories for low-latency accesses, ECC for L1 memory soft error protection, and Andes Custom Extension™ (ACE) to add proprietary instructions to accelerate performance/power consumption critical spots.

N25F's 5-stage pipeline is optimized for high operating frequency and high performance. Features also includes PLIC and vectored interrupts for serving various types of system events, AXI 64-bit or AHB 64/32-bit bus, PowerBrake, QuickNap™ and WFI mode for low power and power management, and JTAG debug interface for development support.

N25F's 5-stage pipeline is optimized for high operating frequency and high performance. Features also includes PLIC and vectored interrupts for serving various types of system events, AXI 64-bit or AHB 64/32-bit bus, PowerBrake, QuickNap™ and WFI mode for low power and power management, and JTAG debug interface for development support.

查看 RISC-V CPU IP With ISO 26262 Full Compliance 详细介绍:

- 查看 RISC-V CPU IP With ISO 26262 Full Compliance 完整数据手册

- 联系 RISC-V CPU IP With ISO 26262 Full Compliance 供应商

Block Diagram of the RISC-V CPU IP With ISO 26262 Full Compliance