You are here:

RISC-V-based AI IP development for enhanced training and inference

Tenstorrent develops AI IP with precision, anchored in RISC-V’s open architecture, delivering specialized, silicon-proven solutions for both AI training and inference. Our platforms are optimized for high performance per watt, ensuring scalable and adaptable technology for all AI-specific workloads.

查看 RISC-V-based AI IP development for enhanced training and inference 详细介绍:

- 查看 RISC-V-based AI IP development for enhanced training and inference 完整数据手册

- 联系 RISC-V-based AI IP development for enhanced training and inference 供应商

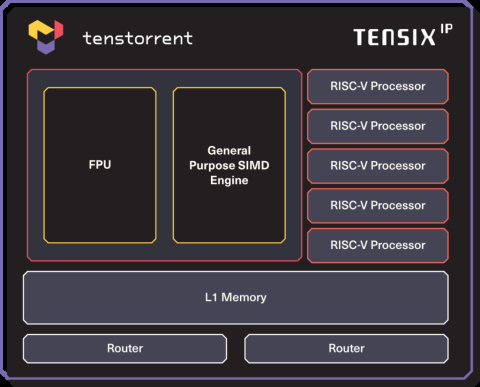

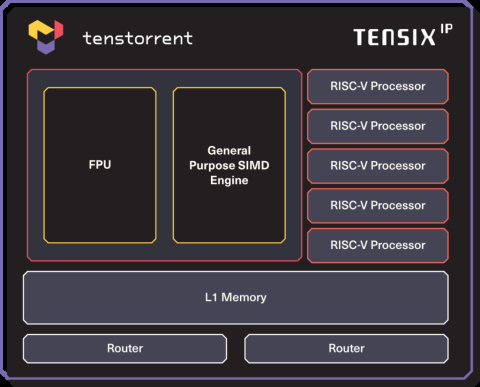

Block Diagram of the RISC-V-based AI IP development for enhanced training and inference

AI IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- NPU IP family for generative and classic AI with highest power efficiency, scalable and future proof

- NPU IP for Embedded AI

- Tessent AI IC debug and optimization

- AI accelerator (NPU) IP - 16 to 32 TOPS

- Complete Neural Processor for Edge AI