MIPI C-PHY v1.2 D-PHY v2.1 TX 3 trios/4 Lanes in TSMC (16nm, 12nm, N7, N6, N5, N3E)

You are here:

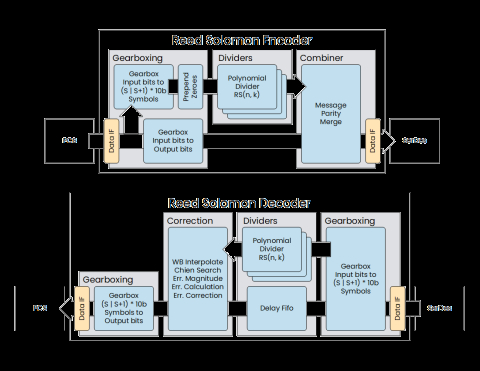

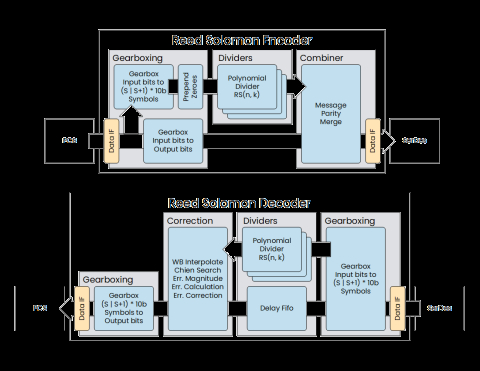

Reed Solomon Forward Error Correction Encoder Decoder

The Reed Solomon Forward Error Correction (RS FEC) IP is a highly optimized and silicon agnostic implementation of the RS FEC encoder and decoder algorithm targeting both ASICs and FPGAs. The algorithm for RS-FEC is used across multiple standards in the industry as listed in the table below. Our solution is optimized towards each application individually to offer the best performance, size, and lowest latency.

The core enables quick and reliable deployment of both the encoder and the decoder. The symbol size (m) is application specific usually 8 or 10 bits and the error correction capability depends on the parity bits attached to the message (n-k)/2 = t.

The IP can be accommodated to any parameter set available and has gone through extensive testing. The IP core is silicon proven, heavily tested in UVM regression environment and has been the key component for all of the IP cores in our portfolio which use RS-FEC encoding.

The core enables quick and reliable deployment of both the encoder and the decoder. The symbol size (m) is application specific usually 8 or 10 bits and the error correction capability depends on the parity bits attached to the message (n-k)/2 = t.

The IP can be accommodated to any parameter set available and has gone through extensive testing. The IP core is silicon proven, heavily tested in UVM regression environment and has been the key component for all of the IP cores in our portfolio which use RS-FEC encoding.

查看 Reed Solomon Forward Error Correction Encoder Decoder 详细介绍:

- 查看 Reed Solomon Forward Error Correction Encoder Decoder 完整数据手册

- 联系 Reed Solomon Forward Error Correction Encoder Decoder 供应商

Block Diagram of the Reed Solomon Forward Error Correction Encoder Decoder