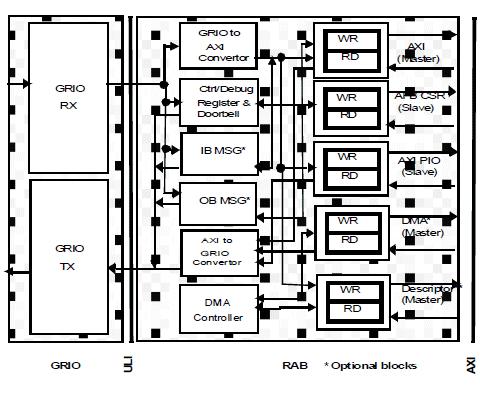

RapidIO to AXI Bridge

The RapidIO to AXI Bridge is a simple, configurable and layered architecture, independent of applications, implementation tools or target technology. The controller architecture is carefully tailored to optimize latency, power consumption, and silicon footprint, making it ideal for cost and performance sensitive applications. The RapidIO to AXI Bridge provides highly scalable bandwidth through a configurable data path width and clock frequency.

The controller's simple, configurable and layered architecture is independent of application logic, PHY designs, implementation tools and, most importantly, the target technology. Mobiveil solution allows the licensees to easily migrate among FPGA, Gate array and Standard cell technologies optimally. Its flexible backend interface makes it easy to be integrated into wide range of applications. Mobiveil solution provides highly scalable bandwidth through configurable lanes, widths and frequencies.

查看 RapidIO to AXI Bridge (RAB) 详细介绍:

- 查看 RapidIO to AXI Bridge (RAB) 完整数据手册

- 联系 RapidIO to AXI Bridge (RAB) 供应商

Block Diagram of the RapidIO to AXI Bridge (RAB)