You are here:

Radio Clock (DCF77) Slave core

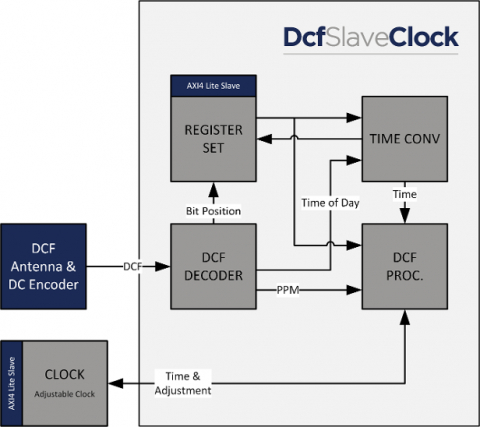

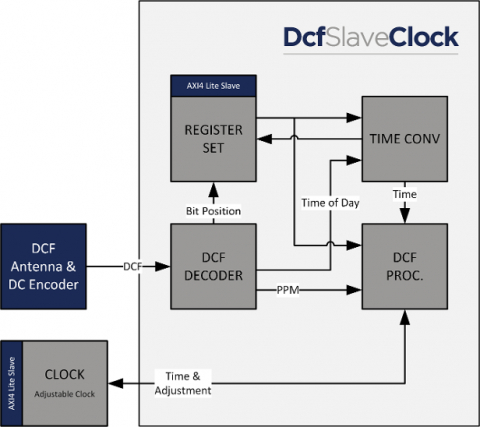

NetTimeLogic’s DCFSlave Clock is a full hardware (FPGA) only implementation of a synchronization core able to synchronize to a DCF signal encoded as PWM. The encoding scheme is the one of the DCF77 sender near Frankfurt, Germany. The whole encoding, algorithms and calculations are implemented in the core, no CPU is required. This allows running DCF synchronization completely independent and standalone from the user application. The core can be configured either by signals or by an AXI4Light-Slave Register interface.

All calculations and corrections are implemented completely in HW.

All calculations and corrections are implemented completely in HW.

查看 Radio Clock (DCF77) Slave core 详细介绍:

- 查看 Radio Clock (DCF77) Slave core 完整数据手册

- 联系 Radio Clock (DCF77) Slave core 供应商

Block Diagram of the Radio Clock (DCF77) Slave core