You are here:

QDRII + SRAM Controller MACO Core

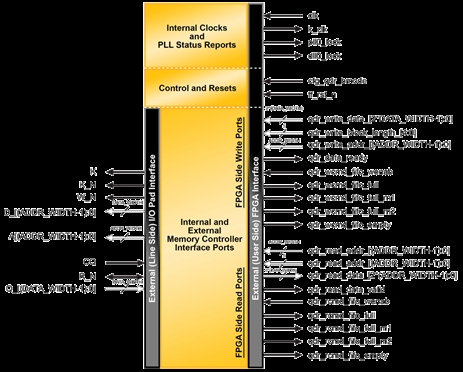

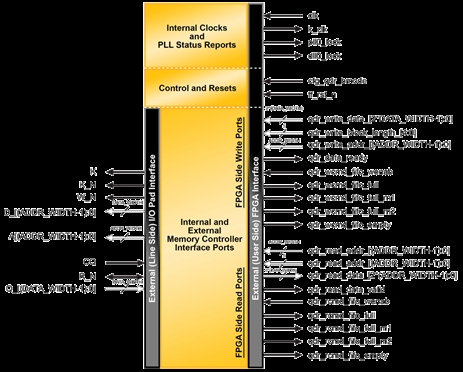

The second generation Quad-Data-Rate (QDRII) Static Random Access Memory (SRAM) Controller is a general purpose memory controller that interfaces with industry standard QDRII and QDRII+ SRAM. The controller can be configured to function in two-word burst or four-word burst modes. It can also be configured to have an 18-bit bus or a 36-bit data bus. The data is transferred on both edges of the clock, doubling the rate of data transfer. Separate read and write data buses again double the data rate.

The QDRII+ IP Core is implemented using both MACO ASIC gates and soft logic in the FPGA array. Since a significant portion of the implementation is in MACO, more of the FPGA Array is left for the user.

Software Requirements

* ispLEVER version 7.0 or later

* MACO design kit

* MACO license file

The QDRII+ IP Core is implemented using both MACO ASIC gates and soft logic in the FPGA array. Since a significant portion of the implementation is in MACO, more of the FPGA Array is left for the user.

Software Requirements

* ispLEVER version 7.0 or later

* MACO design kit

* MACO license file

查看 QDRII + SRAM Controller MACO Core 详细介绍:

- 查看 QDRII + SRAM Controller MACO Core 完整数据手册

- 联系 QDRII + SRAM Controller MACO Core 供应商

Block Diagram of the QDRII + SRAM Controller MACO Core

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software