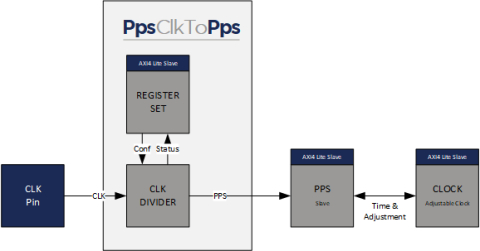

Pulse Per Second (PPS) Clock to PPS core

This core is intended to be used with either external clocks or also SyncE clocks when the frequency shall be adjusted numerically rather than a clock switch.

查看 Pulse Per Second (PPS) Clock to PPS core 详细介绍:

- 查看 Pulse Per Second (PPS) Clock to PPS core 完整数据手册

- 联系 Pulse Per Second (PPS) Clock to PPS core 供应商

Block Diagram of the Pulse Per Second (PPS) Clock to PPS core