Embedded Flash Protection with Hardware Root of Trust and Lite Crypto Engine

查看 Embedded Flash Protection with Hardware Root of Trust and Lite Crypto Engine 详细介绍:

- 查看 Embedded Flash Protection with Hardware Root of Trust and Lite Crypto Engine 完整数据手册

- 联系 Embedded Flash Protection with Hardware Root of Trust and Lite Crypto Engine 供应商

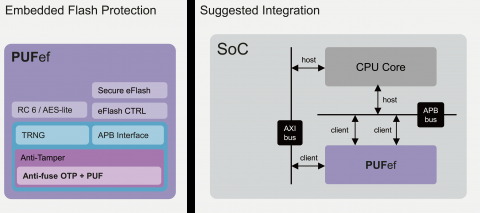

Block Diagram of the Embedded Flash Protection with Hardware Root of Trust and Lite Crypto Engine