You are here:

Processor Development Toolset

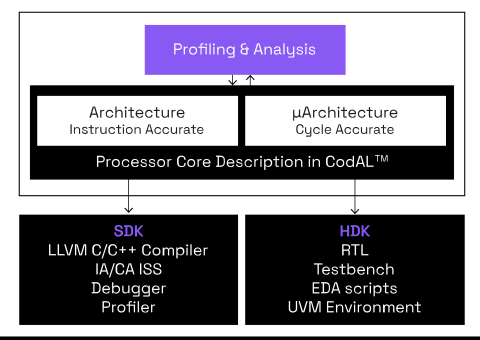

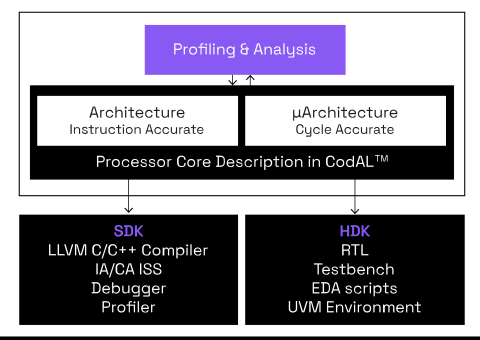

Codasip Studio is a complete set of Electronic Design Automation (EDA) tools for processor design and customization. The level of automation is unmatched on the market, and produces fast and efficient results.

Our approach at Codasip is to automate the development of processor cores by using a high-level description in the CodAL processor description language and generating the design implementation, verification environment, virtual system prototype, and a complete software toolchain using Codasip Studio.

In addition to its design capabilities, Codasip Studio includes powerful multiprocessor programming, debugging and profiling features, enabling the development of complex processor designs with ease.

Codasip Studio is built upon open standards and software including Eclipse, LLVM, Verilog, SystemVerilog, and UVM.

Our approach at Codasip is to automate the development of processor cores by using a high-level description in the CodAL processor description language and generating the design implementation, verification environment, virtual system prototype, and a complete software toolchain using Codasip Studio.

In addition to its design capabilities, Codasip Studio includes powerful multiprocessor programming, debugging and profiling features, enabling the development of complex processor designs with ease.

Codasip Studio is built upon open standards and software including Eclipse, LLVM, Verilog, SystemVerilog, and UVM.

查看 Processor Development Toolset 详细介绍:

- 查看 Processor Development Toolset 完整数据手册

- 联系 Processor Development Toolset 供应商

Block Diagram of the Processor Development Toolset

Processor IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-500 power efficient 32-bit RISC-V processor for embedded applications

- RT-660-FPGA DPA-Resistant Hardware Root-of-Trust Security Processor for Govt/Aero/Defense FIPS-140

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Secure-IC Securyzr(TM) Cyber Escort Unit IP provides real time detection of sero day attacks on processor

- 32-bit Embedded RISC-V Functional Safety Processor