Secure-IC's Securyzr™ Fully Digital Physically Unclonable Function (PUF) - PQC Ready

You are here:

PCS Pipe IP核

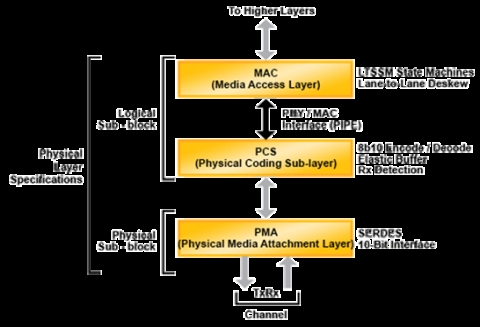

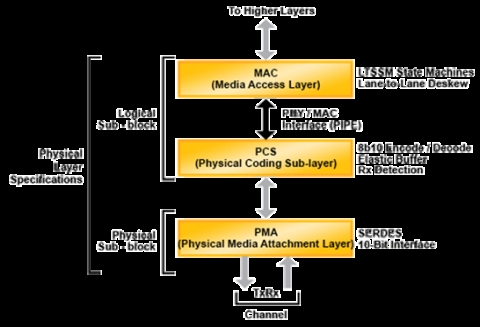

针对PCI Express (PIPE)作为在物理层器件和媒体存取控制器( MAC )层之间的一个标准接口, 以及PCI Express (PCIe )的应用,英特尔定义了PHY接口。PIPE接口允许PCI Express PHY器件和MAC层以分立的形式(用现成的PHY器件)或集成的形式来实现。如下图所示的PCI Express物理层的划分说明了这种灵活性。

莱迪思的PCS PIPE IP核提供的PCI Express PHY器件的功能,符合英特尔的PIPE架构草案1.00版本 (PIPE 1.00版本 ),提供对任何端点的解决方案。PCS PIPE IP核采用整合在LatticeECP3和LatticeECP2M FPGA中的SERDES/PCS。莱迪思的PCS PIPE IP核可以配置为支持一个或四个链路。

莱迪思的PCS PIPE IP核提供的PCI Express PHY器件的功能,符合英特尔的PIPE架构草案1.00版本 (PIPE 1.00版本 ),提供对任何端点的解决方案。PCS PIPE IP核采用整合在LatticeECP3和LatticeECP2M FPGA中的SERDES/PCS。莱迪思的PCS PIPE IP核可以配置为支持一个或四个链路。

查看 PCS Pipe IP核 详细介绍:

- 查看 PCS Pipe IP核 完整数据手册

- 联系 PCS Pipe IP核 供应商

Block Diagram of the PCS Pipe IP核

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software