You are here:

PCIe 5.0 Serdes PHY IP,在 TSMC 12FFC 中经过硅验证

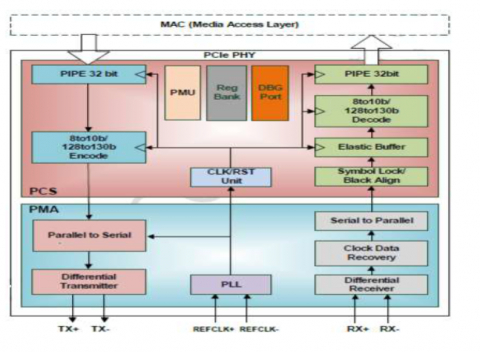

这个外设组件互连快速(PCIe)x4 PHY符合PCIe 5.0基本规范,支持PIPE 5.1接口规范,通过支持额外的PLL控制、参考时钟控制和嵌入式电源门控控制,实现了更低的功耗。此外,这个PHY IP的低功耗模式可以根据不同功耗调整,能够广泛适用于各种场景.

这个PHY IP满足了当今高速芯片芯片、板对板和背板接口的需求,同时具有低功耗和小的工艺尺寸的特点。对于PCIe PHY IP功能的验证能够在NCVerilog模拟软件中使用测试台进行.

这个PHY IP满足了当今高速芯片芯片、板对板和背板接口的需求,同时具有低功耗和小的工艺尺寸的特点。对于PCIe PHY IP功能的验证能够在NCVerilog模拟软件中使用测试台进行.

查看 PCIe 5.0 Serdes PHY IP,在 TSMC 12FFC 中经过硅验证 详细介绍:

- 查看 PCIe 5.0 Serdes PHY IP,在 TSMC 12FFC 中经过硅验证 完整数据手册

- 联系 PCIe 5.0 Serdes PHY IP,在 TSMC 12FFC 中经过硅验证 供应商

Block Diagram of the PCIe 5.0 Serdes PHY IP,在 TSMC 12FFC 中经过硅验证

PCIeIP IP

- PCIe 3.0 Serdes PHY IP, Silicon Proven in TSMC 28HPCP

- PCIe 4.0 Serdes PHY IP, Silicon Proven in TSMC 12FFC

- PCIe 3.1 Serdes PHY IP, Silicon Proven in TSMC 28HPCP

- PCIe 3.0 Serdes PHY IP, Silicon Proven in UMC 28HPC

- PCIe 3.0 Serdes PHY IP, Silicon Proven in UMC 40LP

- PCIe 3.0 Serdes PHY IP, Silicon Proven in UMC 55SP