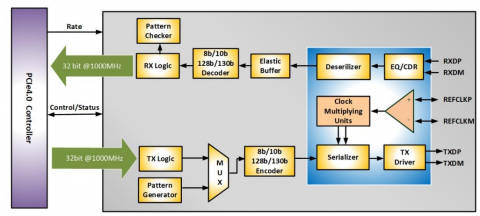

M31 PCIe 5.0 PHY IP provides high-performance, multi-lane capability and low power architecture for high-bandwidth applications. The PCIe 5.0 IP supports a complete range of PCIe 5.0 Base applications and is compliant with the PIPE 5.2 specification. The IP integrates high-speed mixed signal circuits to support 32Gbps PCIe 5.0 traffic and is backward compatible with 16 Gbps PCIe 4.0, 8.0Gbps PCIe 3.1, 5.0Gbps PCIe 2.1 and 2.5Gbps PCIe 1.1 data rates. With the support of TX and RX equalization techniques, the PCIe 5.0 IP is designed to meet the requirements of different channel conditions.