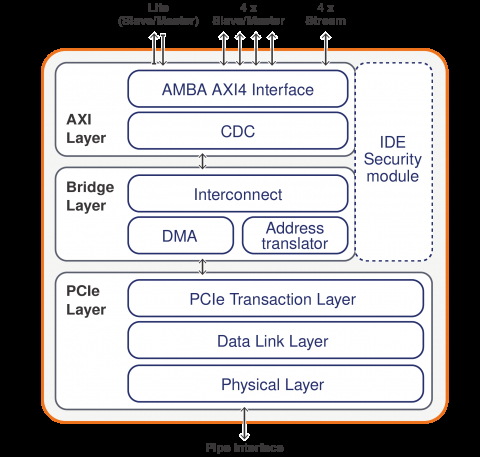

XpressRICH5-AXI是一种可配置和可扩展的PCIe控制器软 IP,专为ASIC和FPGA实现而设计。 XpressRICH5-AXI IP符 合PCI Express 5.0,4.0和3.1 / 3.0规范,以及PCI Express(PIPE)规范的PHY接口和AMBA®AXI™协议规范。此IP可以配置为支持端点,支持根端口和双模拓扑,允 许使用各种模型并向用户公开一个可配置,灵活的 AMBA AXI互连接口。 提供的图形用户界面(GUI)向导 允许设计人员根据其具体要求调整IP,通过启用,禁用 和调整大量参数,包括AXI接口的数量,类型和宽度,PIPE接口宽度、低功耗支持、SR-IOV、ECC、AER等,以获得最佳吞吐量、延迟、面积和功耗。根据应用程序的需求,用户可以选择启用内置的遗留DMA引擎,或者从外部连接DMA引擎,如PLDA的vDMA-AXI DMA。PLDA正在与多个PHY IP供应商和验证IP供应商携手合作,为PCIe 5.0提供一系列32GT/s的集成解决方案。PLDA XpressRICH-AXI控制器IP for PCIe 5.0是ASIC、SoC和FPGA设计人员寻找具有高性能、可靠和可伸缩的AMBA 3 AXI/AMBA 4 AXI互连的企业级PCIe接口解决方案的首选。