You are here:

PCIe 4.0,3.1 / 3.0根端口,端点,双模式,具有Native用 户界面的交换机端口Controller IP核

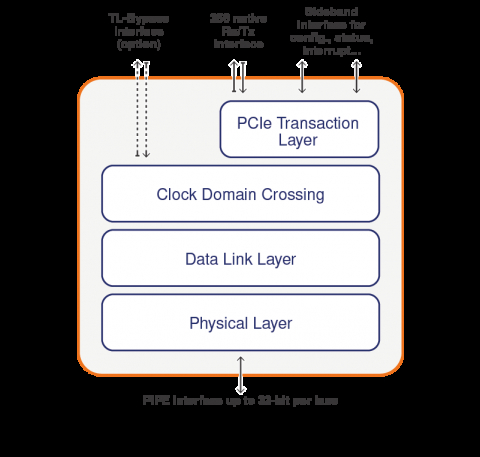

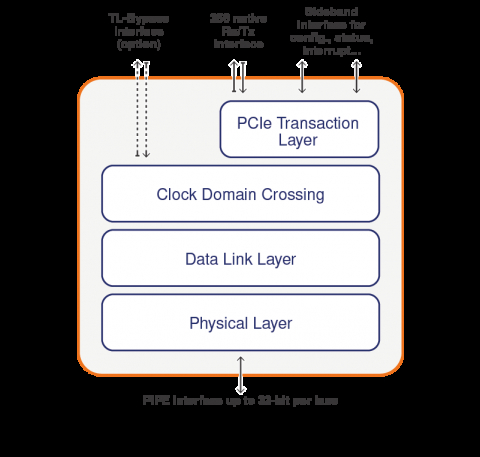

XpressRICH4是一款可配置且可扩展的PCIe controller Soft IP,专为ASIC和FPGA实现而设计。 XpressRICH4 IP符合PCI Express 4.0和3.1 / 3.0规范,以及PCI Express(PIPE)规范 的PHY接口。 IP可以配置为支持端点,根端口,交换机端 口和双模拓扑,允许各种使用模型。提供的图形用户界

面(GUI)向导允许设计人员通过启用,禁用和调整大 量参数来定制IP以满足其精确要求,包括数据路径大小,PIPE接口宽度,低功耗支持,SR-IOV, ECC,AER等,以 实现最佳吞吐量,最低延迟,优化大小和降低功耗。XpressRICH4 IP使用多个PCIe VIP和测试套件进行验证,并在使用各种商用和专有PCIe PHY的数百种设计的生 产芯片中得到验证。 PLDA XpressRICH4 PCIe IP是需要企 业级功能,最高性能,可靠性和可扩展性的设计人员的 首选。

面(GUI)向导允许设计人员通过启用,禁用和调整大 量参数来定制IP以满足其精确要求,包括数据路径大小,PIPE接口宽度,低功耗支持,SR-IOV, ECC,AER等,以 实现最佳吞吐量,最低延迟,优化大小和降低功耗。XpressRICH4 IP使用多个PCIe VIP和测试套件进行验证,并在使用各种商用和专有PCIe PHY的数百种设计的生 产芯片中得到验证。 PLDA XpressRICH4 PCIe IP是需要企 业级功能,最高性能,可靠性和可扩展性的设计人员的 首选。

查看 PCIe 4.0,3.1 / 3.0根端口,端点,双模式,具有Native用 户界面的交换机端口Controller IP核 详细介绍:

- 查看 PCIe 4.0,3.1 / 3.0根端口,端点,双模式,具有Native用 户界面的交换机端口Controller IP核 完整数据手册

- 联系 PCIe 4.0,3.1 / 3.0根端口,端点,双模式,具有Native用 户界面的交换机端口Controller IP核 供应商

Block Diagram of the PCIe 4.0,3.1 / 3.0根端口,端点,双模式,具有Native用 户界面的交换机端口Controller IP核

PCIe IP

- PCIe 5.0 Integrity and Data Encryption Security Module

- PCIe 6.1 Controller

- PCIe 5.0 Serdes PHY IP, Silicon Proven in TSMC 12FFC

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency

- 56G Serdes in 7nm bundled with PCie Gen 5 controller IP