PCIe 2.0 Serdes PHY IP,在 TSMC 28HPCP 中经过硅验证

PCIe2.0 PHY IP 的收发器对低功耗和减小管芯面积功能进行了优化,不需要牺牲性能和高数据传输速率。这个PCIe2.0 PHY身体包含的完整片上物理层收发器电路,也具备静电保护功能(ESD),内置的自测试电路处理抖动问题,动态均衡器电路,确保整体的性能实现高质量的处理结果。.

查看 PCIe 2.0 Serdes PHY IP,在 TSMC 28HPCP 中经过硅验证 详细介绍:

- 查看 PCIe 2.0 Serdes PHY IP,在 TSMC 28HPCP 中经过硅验证 完整数据手册

- 联系 PCIe 2.0 Serdes PHY IP,在 TSMC 28HPCP 中经过硅验证 供应商

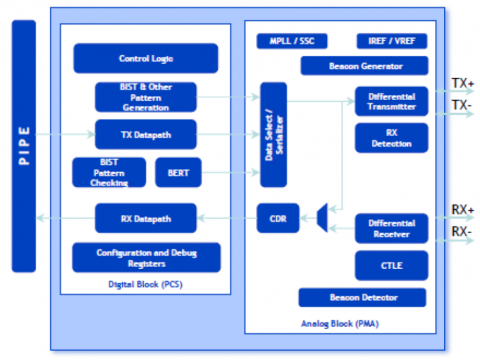

Block Diagram of the PCIe 2.0 Serdes PHY IP,在 TSMC 28HPCP 中经过硅验证