You are here:

PCIe 2.0 End Point IP Core - PCIe with FIFO Interface

The Arasan PCI Express End Point is a high-speed, high-performance, and lowpowerIP core that is fully compliant to the PCI Express Specification 1.1 and 2.0. The IP core is designed for applications in computing, networking, storage, servers, wireless, and consumer electronics. The feature-rich IP core is highly configurable that allows a target design to be implemented with the least number of gates and highest performance.

查看 PCIe 2.0 End Point IP Core - PCIe with FIFO Interface 详细介绍:

- 查看 PCIe 2.0 End Point IP Core - PCIe with FIFO Interface 完整数据手册

- 联系 PCIe 2.0 End Point IP Core - PCIe with FIFO Interface 供应商

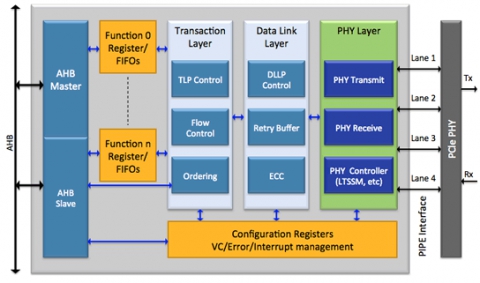

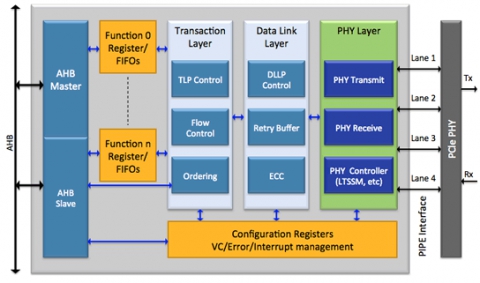

Block Diagram of the PCIe 2.0 End Point IP Core - PCIe with FIFO Interface