You are here:

PCI Express x1、x4 Root Complex Lite IP核

PCI Express是一种高性能、完全可扩展、完整定义的标准,适用于各种计算和通信平台。它已被定义用于提供与现有的PCI驱动和操作系统之间的软件兼容性。作为一种基于数据包的串行技术,PCI Express大大减少了所需的引脚数量,简化了电路板的布线和制造。PCI Express是一种点到点的技术,不同于PCI中的多点通信总线。每个PCI Express器件具有与其相邻器件进行全双工通信的优点,大大提高了总的系统带宽。单线的基本数据速率是32位/33 MHz PCI总线的两倍。4线链路每个方向上的数据速率是传统总线的8倍。

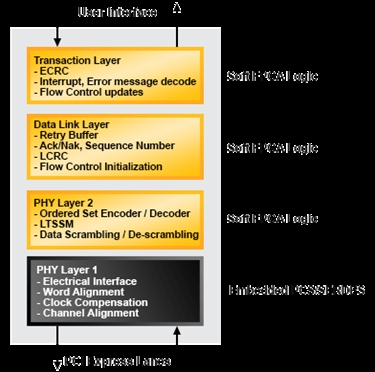

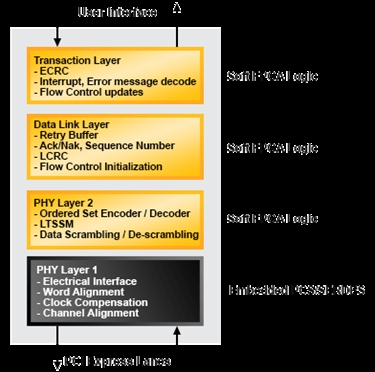

莱迪思的PCI Express Root Complex (RC) Lite核 通过电气SERDES接口、PCI express协议栈的物理层、数据链路层和最小执行层,提供了一个x1或x4 root complex解决方案。该IP是用于简单桥接应用到本地总线root complex 的简易版。该解决方案支持高价值、低功耗LatticeECP3和LatticeECP2M FPGA器件系列。

解决方案

* 从PCI Express演示示例页面,下载演示示例位流。

* 请访问PCI Express解决方案页面,获得其他演示示例、电路板和开发套件。

莱迪思的PCI Express Root Complex (RC) Lite核 通过电气SERDES接口、PCI express协议栈的物理层、数据链路层和最小执行层,提供了一个x1或x4 root complex解决方案。该IP是用于简单桥接应用到本地总线root complex 的简易版。该解决方案支持高价值、低功耗LatticeECP3和LatticeECP2M FPGA器件系列。

解决方案

* 从PCI Express演示示例页面,下载演示示例位流。

* 请访问PCI Express解决方案页面,获得其他演示示例、电路板和开发套件。

查看 PCI Express x1、x4 Root Complex Lite IP核 详细介绍:

- 查看 PCI Express x1、x4 Root Complex Lite IP核 完整数据手册

- 联系 PCI Express x1、x4 Root Complex Lite IP核 供应商

Block Diagram of the PCI Express x1、x4 Root Complex Lite IP核

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software