You are here:

PCI Express PHY serial link PIPE Transceiver IP cell/hard macro

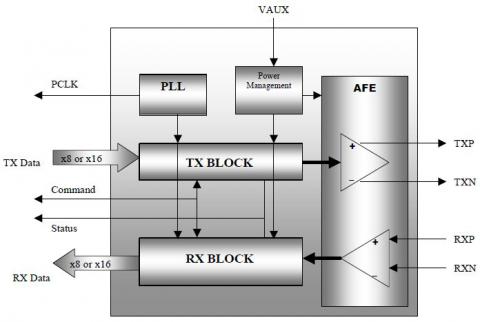

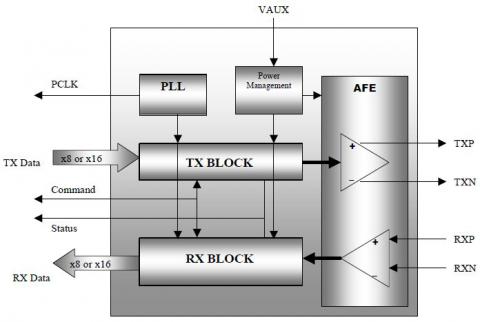

SMS5000 is a fully integrated CMOS transceiver that handles the full Physical Layer PCI Express protocol and signaling. It contains all necessary AFE (Analog Front End), Clock synthesis, Clock Recovery, Serializer, De-serializer, Comma detect for 8B/10B encoded data and frame alignment functionalities. Digital controller interface is realized with a 8-bit parallel operation (Optional 16-bit Interface) that allows use of 250 MHz reference Clock. The transceiver includes Receiver Detection, Beacon Generation, Beacon Detection and Signal Detect capability compliant with PCI Express Specification requirements and provides Short Circuit Protection to ground for outputs. SMS5000 also includes calibrated Transmitter and Receiver Termination Resistors compliant with the requirements of the PCI Express Base 1.0a Specification.

SMS5000 does not require any external Loop filter capacitor(s) for clock Synthesis PLL or Clock recovery circuitry making it immune to PCB related noise typically encountered, and provides a completely integrated solution.

SMS5000 does not require any external Loop filter capacitor(s) for clock Synthesis PLL or Clock recovery circuitry making it immune to PCB related noise typically encountered, and provides a completely integrated solution.

查看 PCI Express PHY serial link PIPE Transceiver IP cell/hard macro 详细介绍:

- 查看 PCI Express PHY serial link PIPE Transceiver IP cell/hard macro 完整数据手册

- 联系 PCI Express PHY serial link PIPE Transceiver IP cell/hard macro 供应商

Block Diagram of the PCI Express PHY serial link PIPE Transceiver IP cell/hard macro

PCI-Express PIPE PHY Transceiver IP

- 1 to 64 Gbps PCI-Express (PCIe) 6.0 and CXL 3.0 PHY

- USB 3.1 Gen1/Gen2 PHY IP, Silicon Proven in UMC 28HPC

- USB 3.1 Gen1/Gen2 PHY IP, Silicon Proven in SMIC 14SF+

- USB 3.2 Gen2 PHY IP, Silicon Proven in UMC 28HPC

- USB 3.1 Gen1/Gen2 PHY IP, Silicon Proven in TSMC 28HPC+

- PCIe 4.0 PHY in TSMC (28nm, 16nm, 12nm, N7, N3P)