You are here:

P1619/802.1ae (MACSec) GCM/XEX/XTS-AES Core

General Description LAN security standard IEEE 802.1ae (MACSec) uses AES cipher in the GCM mode, while the disk/tape encryption standard IEEE P1619 uses the XEX/XTS mode. Since GCM and XEX/XTS share some of their basic components, a combo GCM/XEX/XTS core is not much larger than a dedicated core for either of the modes.

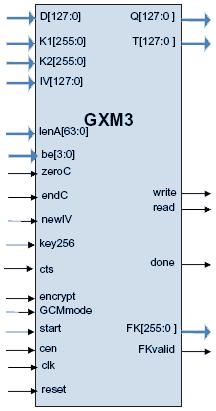

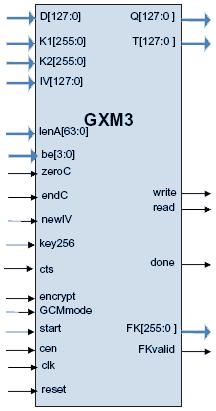

The GXM3 core is tuned for mid-performance P1619 and 802.1ae applications at the data rates of 2-3 Gbps and higher. The core contains the base AES core AES1 and is available for immediate licensing.

The design is fully synchronous and available in both source and netlist form.

The GXM3 core is tuned for mid-performance P1619 and 802.1ae applications at the data rates of 2-3 Gbps and higher. The core contains the base AES core AES1 and is available for immediate licensing.

The design is fully synchronous and available in both source and netlist form.

查看 P1619/802.1ae (MACSec) GCM/XEX/XTS-AES Core 详细介绍:

- 查看 P1619/802.1ae (MACSec) GCM/XEX/XTS-AES Core 完整数据手册

- 联系 P1619/802.1ae (MACSec) GCM/XEX/XTS-AES Core 供应商

Block Diagram of the P1619/802.1ae (MACSec) GCM/XEX/XTS-AES Core

combo IP

- LPDDR Combo Controller - LPDDR4X/4 & LPDDR5T/5X/5

- MIPI D-PHY / C-PHY Combo IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- MIPI C-PHY/D-PHY Combo RX+ IP (4.5Gsps/4.5Gbps) in TSMC N5

- MIPI C-PHY/D-PHY Combo CSI-2 RX+ IP (6.0Gsps/trio, 4.5Gbps/lane) in TSMC N6

- MIPI C-PHY/D-PHY Combo TX+ IP 4.5Gsps/4.5Gbps in TSMC N5

- MIPI C-PHY/D-PHY Combo Universal IP, 4.5Gsps/4.5Gbps in TSMC 22ULP