You are here:

OSU/OTN processor, optimized for E1/STM1/OC3/STM4/OC12/FE/GE services over OTU0/OTU1 lines

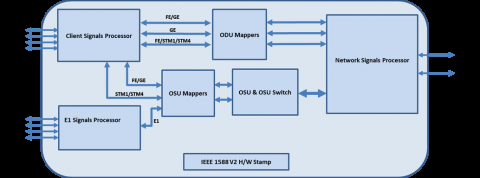

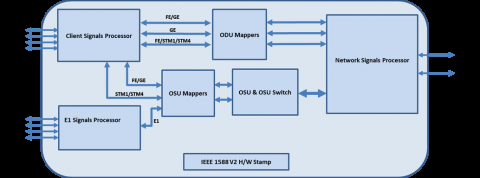

The TPS3204MP OSU processor is an IP Core solution designed for Xilinx FPGAs. TPS3204MP processors accept 4x STM1/STM4/FE/GE and 4x E1 client signals, process and present them to either OSU or ODU containers for their transport over OTU0/OTU1 bearers. The OTU line signals can be configured in a variety of protection configurations: 1+1, Linear, Ring. TPS3204MP processors support OTU, ODU and OSU signal overheads. For Ethernet client-services, Ethernet bandwidth limiting is provided, along with integrated IEEE 1588 V2 H/W Time Stamping. TPS3204MP processors support hitless bandwidth adjustment of OSU containers carrying Ethernet information. Integrated HDLC controllers can be assigned to GCC in-band communications channels. TPS3204MP processors are offered as complete turn-key solutions, including built-in jitter filters, without necessitating external PLLs.

查看 OSU/OTN processor, optimized for E1/STM1/OC3/STM4/OC12/FE/GE services over OTU0/OTU1 lines 详细介绍:

- 查看 OSU/OTN processor, optimized for E1/STM1/OC3/STM4/OC12/FE/GE services over OTU0/OTU1 lines 完整数据手册

- 联系 OSU/OTN processor, optimized for E1/STM1/OC3/STM4/OC12/FE/GE services over OTU0/OTU1 lines 供应商

Block Diagram of the OSU/OTN processor, optimized for E1/STM1/OC3/STM4/OC12/FE/GE services over OTU0/OTU1 lines