You are here:

Non-Power-of-Two FFT

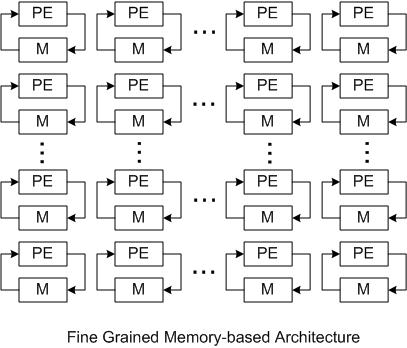

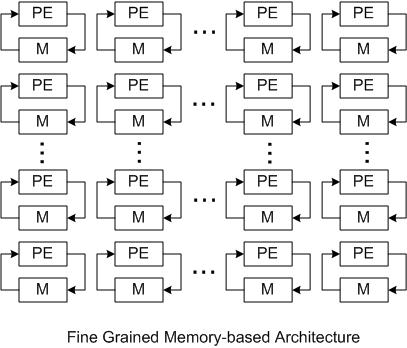

The transform computation is based on a new matrix formulation of the discreet Fourier transform1 (DFT) which decomposes it into structured sets of b-point DFTs. This avoids the inherent irregularities of the usual signal flow graph approach which typically requires complex commutators or permutation circuits, variable memory blocks, large butterfly units, global interconnections, and stage-to-stage differences, all of which degrade performance and require extra logic resources. Centar’s approach uses a small, regular, locally connected array, that keeps interconnect delays lower than cell delays, leading to high clock speeds/throughput and minimizes power. Because the circuit has a "memory based" architecture2, it is programmable so that a range of transform can be performed on the same array given adequate memory resources. (Data provided here applies to LTE SC-FDMA DFT transform size requirements). Finally, it includes a low overhead hybrid floating-point feature that increases dynamic range for a given fixed-point word size.

查看 Non-Power-of-Two FFT 详细介绍:

- 查看 Non-Power-of-Two FFT 完整数据手册

- 联系 Non-Power-of-Two FFT 供应商

Block Diagram of the Non-Power-of-Two FFT

DFT IP

- Discrete Fourier Transform (DFT)

- 32Gbps, 7/15/31 order, Pseudo Random Bit Sequence Generator, Checker, Error Counter

- 32Gbps, 7/15 order, Pseudo Random Bit Sequence Generator, Checker, Error Counter

- 32Gbps, 31 order, Pseudo Random Bit Sequence Generator, Checker, Error Counter

- Fast Fourier Transformation

- High performance FFT with Gsps throughput