You are here:

Multiprocessor, 4-Way Simultaneous Multithreading

特色

- Efficient Throughput

- Efficient data-centric processing with simultaneous multi-threading (SMT), low latency and deterministic data access

- 3-Wide, 9-stage, in-order pipeline with 1-, 2-, 4-way SMT

- RISC-V Compliant ISA

- RV64GHZ + Bitmanip Zba and Zbb, + CMO Extension

- MIPS User-Defined Instructions (UDI)—Cache and TLB management, Performance enhancements and DVM (Distributed Virtual Memory) support

- Optional 64KB Data ScratchPad RAM (DSPRAM) for real-time, low-latency applications

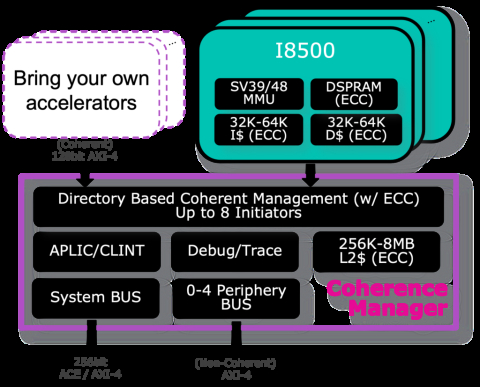

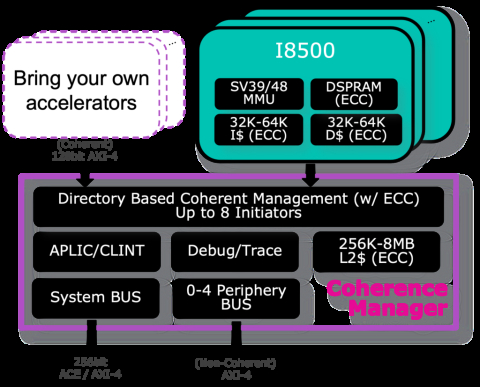

- Coherence Manager

- Support for up to 8 coherent initiators comprising of either MIPS RISC-V Processors or 3rd party accelerators

- Cluster Level-2 Cache L2$ up to 8MB

- HW pre-fetch, widened busses, reduced latency

- System interface:

- ACE or AXI: 256-bit system bus

- Optional: Non-coherent periphery bus (up to 4 ports)

查看 Multiprocessor, 4-Way Simultaneous Multithreading 详细介绍:

- 查看 Multiprocessor, 4-Way Simultaneous Multithreading 完整数据手册

- 联系 Multiprocessor, 4-Way Simultaneous Multithreading 供应商

Block Diagram of the Multiprocessor, 4-Way Simultaneous Multithreading

RISC-V IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-500 power efficient 32-bit RISC-V processor for embedded applications

- ARC-V RHX-105 dual-issue, 32-bit RISC-V processor for real-time applications (multi-core)

- ARC-V RMX-100 ultra-low power 32-bit RISC-V processor for embedded applications

- ARC-V RHX-100 dual-issue, 32-bit single-core RISC-V processor for real-time applications

- 32-bit Embedded RISC-V Functional Safety Processor