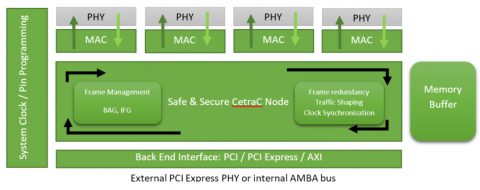

Multi Protocol Endpoint IP Core for Safe and Secure Ethernet Network

It brings a high performance, low latency, safe and cyber-secure link between your software application and the ARINC664p7/Ethernet network.

The CetraC technology is fully compliant with ARINC664 Part 7 and Ethernet standards. It allows both cyclic and event-driven communications in full duplex. A 100% hardware solution with embedded ARINC664 Part 7 redundancy management feature to free more power to your CPU.

It uses a PCI, PCI Express or AXI backend interface to connect to a large portfolio of processors within a very short Time To Market.

By using our CetraC technology you get a safe and cyber secure link from your end user software application up to the network with the smaller footprint in the market.

The IEEE1588 PTPV2 protocol is also available at any port to synchronize the overall devices connected to the network. The CetraC EndSystem IP core acts as GrandMaster or simply distributes the clock to each connected equipment requiring a common clock.

Several IP core switches can be connected together through a 10Gbps optical fiber link to create any of the three kinds of flexible network architectures for critical systems:

• High speed redundant ring architecture (at up to 10Gbps)

• High speed hierarchical architecture (at up to 10Gbps)

• Mesh network by mixing the two previous architectures."

查看 Multi Protocol Endpoint IP Core for Safe and Secure Ethernet Network 详细介绍:

- 查看 Multi Protocol Endpoint IP Core for Safe and Secure Ethernet Network 完整数据手册

- 联系 Multi Protocol Endpoint IP Core for Safe and Secure Ethernet Network 供应商

Block Diagram of the Multi Protocol Endpoint IP Core for Safe and Secure Ethernet Network

Video Demo of the Multi Protocol Endpoint IP Core for Safe and Secure Ethernet Network

CetraC Video Channel