You are here:

MIPI M-PHY in TSMC 65LP

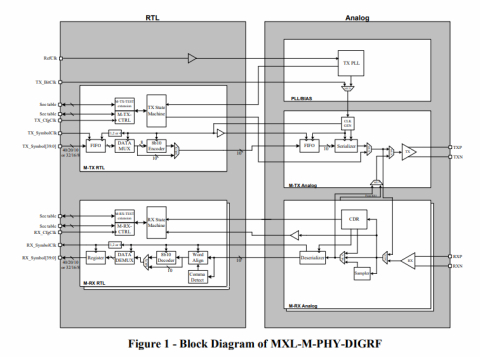

The MXL-M-PHY-DIGRF is a high-frequency low-power, low-cost, Physical Layer IP that supports the MIPI® Alliance Standard for M-PHY and DigRF. The IP can be used as a physical layer for the Baseband to RFIC interface. It supports the DigRF v4 standard.

By using efficient BURST mode operation with scalable speeds, significant power savings can be obtained.

Selection of signal slew rate and amplitude allows reduction of EMI/RFI, while maintaining low bit error rates. The core employs Mixel’s Logarithmic approach, enabling efficient implementation of multiple configurations.

By using efficient BURST mode operation with scalable speeds, significant power savings can be obtained.

Selection of signal slew rate and amplitude allows reduction of EMI/RFI, while maintaining low bit error rates. The core employs Mixel’s Logarithmic approach, enabling efficient implementation of multiple configurations.

查看 MIPI M-PHY in TSMC 65LP 详细介绍:

- 查看 MIPI M-PHY in TSMC 65LP 完整数据手册

- 联系 MIPI M-PHY in TSMC 65LP 供应商

Block Diagram of the MIPI M-PHY in TSMC 65LP

MIPI M-PHY IP

- MIPI M-PHY G4 Type 1 2Tx2RX in TSMC (16nm, 12nm, N7, N6, N5, N4, N3A, N3E)

- MIPI M-PHY - TSMC 40nm

- UFS 4.0 Host Controller compatible with M-PHY 5.0 and UniPro 2.0

- MIPI M-PHY HS-G4 IP (M-PHY v4.1) in TSMC 40G

- UFS 3.0 Host Controller with AES Encryption compatible with M-PHY 4.0 and UniPro 1.8

- MIPI M-PHY v4.1/v3.1 IP in TSMC(5nm, 6nm, 7nm, 12nm,16nm, 22nm, 28nm, 40nm, and 55nm)